Rincon Research Corporation - FPGA Development

```

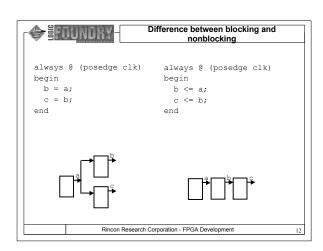

Verilog has 2 types of assignments to a register datatype

Blocking ( a = b)

Nonblocking (a <= b)

Blocking Assignments

Performed immediately (simulation blocks)

Nonblocking Assignments

Performed after all active events in the event queue

```

```

Simplified Verilog Simulation Reference Model

In all the examples that foliow, T refers to the current simulation time, and all events are held in the event queue, ordered by simulation time. while (there are events) {

if (there are active events) {

E = any active event;

if (E is an update event) {

update the modified object;

add evaluation events for sensitive processes to event queue;

}

else { // this is an evaluation event, so ...

evaluate the process;

add update events to the event queue;

}

}

else if (there are nonblocking update events) {

activate all nonblocking update events;

}

else {

advance T to the next event time;

activate all inactive events for time T;

}

}

Rincon Research Corporation - FPGA Development 10

```

```

| Module test (a, pop, clk, rst); input [32:0] a; input [32:0] a; input [6:0] pop; reg [6:0] pop; reg [6:0] pop; always @ (posedge clk or posedge rst) begin if (rst) begin pop <= 0; end else begin pop <= a[0] + a[1] + a[2] + a[3] + a[4] + a[5] + a[6] + a[7] + a[8] + a[9] + a[10] + a[11] + a[12] + a[13] + a[14] + a[15] + a[23] + a[24] + a[25] + a[25] + a[26] + a[27] + a[28] + a[29] + a[31] + a[31]; end end end endmodule | Rincon Research Corporation - FPGA Development | 14

```

```

| Population Count Pipelined (2)

| module test (a, pop, clk, rst); | else begin | p1 <= a[0] + a[1] + a[2] + a[3]; | p2 <= a[4] + a[5] + a[6] + a[7]; | p3 <= a[8] + a[9] + a[10] + a[10] + a[11]; | p3 <= a[8] + a[9] + a[10] + a[11]; | p3 <= a[8] + a[9] + a[10] + a[11]; | p4 <= a[12] + a[13] + a[14] + a[15]; | p5 <= a[16] + a[17] + a[18] + a[19]; | p5 <= a[16] + a[17] + a[18] + a[19]; | p6 <= a[20] + a[21] + a[22] + a[23]; | p7 <= a[24] + a[25] + a[26] + a[27]; | p8 <= a[28] + a[29] + a[29] + a[30] + a[31]; | p7 <= a[28] + a[29] + a[29] + a[30] + a[31]; | p8 <= a[28] + a[29] + a[29] + a[30] + a[31]; | p8 <= a[28] + a[29] + a[29] + a[30] + a[31]; | p9 <= 0; | p0 <= 0; | p0 <= q1 + q2 | p1 + q2 | p4 | p4; | p1 + q2 | p3 | p4; | p1 + q2 | p4 | p4; | p1 + q2 |

```

```

Population Count Retimed

import (13:0) a.

imput (13:0) pop;

reg (6:0) pop;

reg (6:0) pop;

reg (6:0) pop;

pop (= 0;

pl (

```

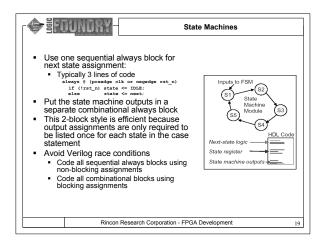

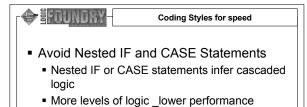

- Evaluate late-arriving signals lastWhen nested IFs are necessary, put critical

- input signals on the first (outer) IF statement

■ The critical signal ends up in the last logic stage

Rincon Research Corporation - FPGA Development

Rincon Research Corporation - FPGA Development