# POST-SILICON BUG LOCALIZATION IN PROCESSORS

TECHNICAL REPORT V2.0

## ABSTRACT

For complex integrated circuits, pre-silicon verification alone is inadequate in ensuring that manufactured chips do not contain logic and electrical bugs. Post-silicon validation, which operates samples of manufactured chips in application environments to validate correct behaviors across specified operating conditions, is essential. According to industry reports, post-silicon validation is becoming very expensive. A major bottleneck in post-silicon validation is the bug localization step which involves identifying hardware bug locations and short functional stimuli that can expose detected bugs. For example, it may take several days to weeks to localize an electrical bug that may arise due to incorrect interactions between a design and the operating conditions.

This report presents IFRA (Instruction Footprint Recording & Analysis), a new technique for post-silicon bug localization in processors, which overcomes cost and scalability challenges of existing techniques. During normal operation of a processor in a postsilicon validation setup, special on-chip recorders collect information about flows of instructions through the processor and what the instructions did as they passed through various design blocks. Upon system failure, such as a crash, the recorded information is scanned out and analyzed offline using special self-consistency-based analysis techniques to localize hardware bugs. IFRA provides two major benefits over traditional techniques: (1) it does not require bugs to be reproduced at the system-level and (2) it does not require system-level simulation. Evaluation of IFRA on an open-source microarchitectural simulator modeling Alpha 21264 demonstrates high bug localization accuracy (96%) at low area overhead (1%).

Applying IFRA to new microarchitectures can be challenging because it requires some degree of manual effort. This report presents a new BLoG (Bug Localization Graph) technique which is a step towards automated application of IFRA. Evaluation of BLoG-assisted IFRA on an industrial microarchitectural simulator modeling Intel® Core<sup>TM</sup> i7, a state-of-the-art complex commercial processor, demonstrates its effectiveness (90% bug localization accuracy) and practicality.

# TABLE OF CONTENTS

| List of tables                                                    | vii  |

|-------------------------------------------------------------------|------|

| List of figures                                                   | viii |

| Chapter 1. Introduction                                           | 1    |

| 1.1 Post-Silicon Validation Background                            | 1    |

| 1.2 Bug Localization Background                                   | 3    |

| 1.3 Contributions                                                 | 4    |

| 1.4 Outline                                                       | 5    |

| Chapter 2. Post-Silicon Bug Localization in Processors Using IFRA | 6    |

| 2.1 Target Processor Model                                        | 8    |

| 2.2 IFRA Hardware Support                                         | 10   |

| 2.2.1 Instruction Footprint Recorder                              | 12   |

| 2.2.2 ID-assignment Unit                                          | 14   |

| 2.2.3 Post-trigger Generator                                      | 16   |

| 2.3 Post-analysis Techniques                                      |      |

| 2.3.1 Formatting Scanned-out Footprints                           | 20   |

| 2.3.2 Footprint Linking                                           | 22   |

| 2.3.2.1 Footprint Pointer                                         | 24   |

| 2.3.2.2 <location, footprint=""> Pair</location,>                 | 25   |

| 2.3.2.3 Follow_link() Operator                                    | 25   |

| 2.3.2.4 Footprint Pointer Comparison Operator                     | 26   |

| 2.3.3 High-level Analysis                                         | 27   |

| 2.3.3.1 Data-dependency Analysis                                  |      |

| 2.3.3.2 Control-flow Analysis                                     |      |

| 2.3.3.3 Data-transfer Analysis                                    | 31   |

| 2.3.3.4 Instruction-flow Analysis                                 |      |

| 2.3.4 Low-level Analysis                                          | 35   |

| 2.3.5 Bug-exposing Stimulus                                       | 35   |

| 2.4 Results                                                       |      |

| 2.5 Related Work                                               |    |

|----------------------------------------------------------------|----|

| 2.6 Conclusions                                                | 41 |

| Chapter 3. Application of IFRA using BLoG                      | 42 |

| 3.1 BLoG Components                                            | 44 |

| 3.1.1 BLoG Node Types                                          | 44 |

| 3.1.2 BLoG Edge Attributes                                     | 46 |

| 3.2 BLoG Construction                                          | 48 |

| 3.3 BLoG Traversal                                             | 50 |

| 3.3.1 Footprint-Propagation Rules                              | 53 |

| 3.3.2 Location-Propagation Rules                               | 55 |

| 3.4 Evaluation on an Industrial Simulator                      | 68 |

| 3.4.1 Simulation Framework and Methodology                     | 69 |

| 3.4.2 Results                                                  | 72 |

| 3.5 Related Work                                               | 74 |

| 3.6 Conclusions                                                | 75 |

| Chapter 4. Concluding Remarks                                  | 76 |

| References                                                     | 77 |

| Appendix A: Footprint Linking Algorithm                        | 81 |

| A.1 Assumptions on the Target Processor                        | 81 |

| A.2 Distinguishing Footprints with Identical IDs               | 82 |

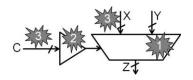

| A.3 Identification of Uncommitted Instructions                 | 85 |

| A.3.1 Uncommitted Instructions in In-order Pipeline Stages     | 85 |

| A.3.2 Uncommitted Instructions in Out-of-order Pipeline Stages | 89 |

| A.3.2.1 Identification of Younger-isolating Row                | 91 |

| A.3.2.2 Identification of Older-isolating Row                  | 91 |

| Appendix B: Low-Level Analysis Decision Diagram for IFRA       | 94 |

# LIST OF TABLES

| Number                                                                | Page |

|-----------------------------------------------------------------------|------|

| Table 1.1. Pre-silicon verification vs. post-silicon validation.      | 1    |

| Table 2.1. Auxiliary information for Alpha microarchitecture          | 13   |

| Table 2.2. Failure scenarios and post-triggers.                       | 17   |

| Table 2.3. Error injection bits.                                      |      |

| Table 2.4. IFRA bug localization summary.                             |      |

| Table 2.5. IFRA vs. existing techniques.                              | 40   |

| Table 3.1: Location-propagation rules for a Random-access type.       | 65   |

| Table 3.2. Auxiliary information for Intel Core i7 microarchitecture. | 68   |

| Table 3.3: Error injection sites                                      | 70   |

| Table 3.4. BLoG node type distribution for Intel Core i7.             | 71   |

| Table 3.5. BLoG-assisted IFRA bug localization summary.               | 72   |

| Table 3.6. Causes of complete miss.                                   | 72   |

| Table 3.7. Summary of manual effort reduced using BLoG                | 73   |

# LIST OF FIGURES

| Number                                                                         | Page |

|--------------------------------------------------------------------------------|------|

| Fig. 2.1. Post-silicon bug localization flow using IFRA.                       | 6    |

| Fig. 2.2. Superscalar processor augmented with recording infrastructure        | 11   |

| Fig. 2.3. Internal structure of a footprint recorder.                          | 12   |

| Fig. 2.4. ID-assignment unit for a 2-way processor                             | 15   |

| Fig. 2.5. Post-analysis summary.                                               | 19   |

| Fig. 2.6. Aligning four unwrapped circular buffers for a 4-way pipeline stage  | 21   |

| Fig. 2.7. Fetch-stage footprint vector augmented with instruction words        | 21   |

| Fig. 2.8. Footprint linking, with a max number of 2 instructions in flight     | 23   |

| Fig. 2.9. Flushed / flush-causing instructions in fetch stage footprint vector | 23   |

| Fig. 2.10. Footprint pointer and direction of pointer increment.               | 24   |

| Fig. 2.11. Footprints indicating cycles within a pipeline stage                | 25   |

| Fig. 2.12. Data-dependency analysis example.                                   | 29   |

| Fig. 3.1. Bug localization flow using BLoG-assisted IFRA vs. original IFRA     | 43   |

| Fig. 3.2. Eight BLoG node types.                                               | 45   |

| Fig. 3.3. Relationship between BLoG edge attributes.                           | 46   |

| Fig. 3.4. Example <edge, dependency="" edge=""> pairs.</edge,>                 | 47   |

| Fig. 3.5. Example starting edge for a control-flow analysis inconsistency      | 50   |

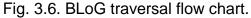

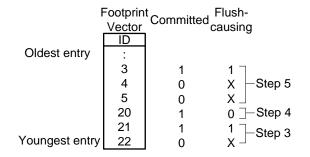

| Fig. 3.6. BLoG traversal flow chart.                                           | 52   |

| Fig. 3.7. Node traversal flow chart.                                           | 52   |

| Fig. 3.8. Location-propagation rules for a Select-type node                    | 59   |

| Fig. A.1. Example footprint vector with labels ( <i>n</i> =8).                 |      |

## **CHAPTER 1. INTRODUCTION**

## **1.1 POST-SILICON VALIDATION BACKGROUND**

With increasing chip complexity and shortening time-to-market, chip developers are facing progressively more difficult challenges in ensuring their chips to be free of hardware bugs before shipment. Hardware bugs are detected either before chip fabrication, during *pre-silicon verification*, or after fabrication, during *post-silicon validation*. Pre-silicon verification [Clarke 99][Dill 98][Schelle 10] checks the design for its correct functionality using simulation / emulation techniques or using formal methods. Post-silicon validation involves operating manufactured chips in actual application environments to check for their correct behaviors across specified operating conditions (*e.g.*, voltage, temperature and frequency).

Table 1.1 compares and contrasts the two phases of chip development. Accessing internal signals of a physical chip is difficult as it is done indirectly through package pins or through special-purpose built-in hardware (*e.g.*, Boundary-scan JTAG interface [TI 97]). Pre-silicon verification is free of this problem because any arbitrary signal can be probed in a software environment. Fixing physical bug is expensive and can cost multiple silicon re-spins, which involves redesigning the mask (costing \$1 million for sub-90nm technology [Ying 05]) to remanufacture the chip with corrections.

|                         | Pre-silicon<br>Verification | Post-Silicon<br>Validation |  |  |

|-------------------------|-----------------------------|----------------------------|--|--|

| Signal access           | (+) Easy                    | (-) Limited                |  |  |

| Bug fixes               | (+) Cheap                   | (-) Expensive              |  |  |

| Electrical bugs         | (-) Difficult to model      | (+) Already present        |  |  |

| Problem detection speed | (-) Slow                    | (+) Fast                   |  |  |

Table 1.1. Pre-silicon verification vs. post-silicon validation.

Although pre-silicon verification is essential, and has traditionally been the main tool for detecting hardware bugs, post-silicon validation is becoming increasingly important for the following three reasons:

- With increasing chip complexity, several electrical interactions are becoming significant, e.g., signal integrity, cross-talk and power-supply noise, temperature effects, etc. Accurate modeling of all these physical effects is usually very difficult during pre-silicon verification;

- With increasing design complexity (e.g., prevalence of adaptive power management), simulations and emulations are not fast enough (orders of magnitude slower than physical chip [Krupnova 04]) to explore many possible configurations and corner cases;

- 3) With increasing process variations, designing for the worst case leads to unacceptable power and/or performance. Chips not designed for the worst case must be validated after fabrication [Yerramilli 06].

According to recent industry reports, post-silicon validation is becoming significantly expensive. Intel reported a headcount ratio of 3:1 for design vs. post-silicon validation [Patra 07]. According to [Abramovici 06], post-silicon validation may consume 35% of average chip development time. [Yeramilli 06] observes that post-silicon validation costs are rising faster than the design costs.

Post-silicon validation involves four steps:

- 1) *Bug detection*: Detecting a problem by running a test, such as end-user applications or functional tests, until a *system failure* (chip in a system returns a fatal exception or stops functioning altogether).

- Bug localization: Localizing the problem to a small region from the system failure, e.g., a bug in an adder inside an ALU of a complex processor. The stimulus that exposes the bug, e.g., the particular 10 lines of code from some application, is also important.

- 3) *Bug root-cause*: Identifying the root cause of the problem. For example, an electrical bug may be caused by power-supply noise slowing down a circuit path resulting in an error at the adder output.

- Bug fixing: Fixing or bypassing the problem by microcode patching [Chang 07] [Goddard 95] [Sarangi 07][Wagner 06], circuit editing [Livengood 99], or, as a last resort, re-spinning using a new mask.

Josephson [Josephson 06] points out that the second step, bug localization, dominates post-silicon validation effort and costs. Hence, this report focuses on bug localization.

### **1.2 BUG LOCALIZATION BACKGROUND**

The bottleneck in post-silicon validation can be further narrowed down by considering the types of bugs being localized. There are two types of bugs that design and validation engineers worry about:

- Logic bugs (also called *functional bugs*): Bugs caused by design errors. While many functional bugs get detected during pre-silicon verification, a small percentage of them get exposed during post-silicon validation due to increasing design complexity and design schedule constraints.

- Electrical bugs (also called *circuit marginalities*): Bugs caused by the interactions between the design and the electrical effects, such as cross-talk and power-supply noise. Such bugs generally manifest themselves only under certain operating conditions (temperature, voltage, frequency). Examples include setup and hold time problems.

There are two major challenges faced by most bug localization techniques used today that limit their scalability for future systems:

1) *System-level failure reproduction*: When a failure is detected while using a chip in a system, most existing techniques require the failure to be reproducible. Failure reproduction involves returning the chip to an error-free state, and re-executing

the failure-causing stimulus (including test segment, interrupts, and operating conditions) to reproduce the same failure. Unfortunately, many electrical bugs are hard to reproduce [Patra 07] due to presence of asynchronous I/Os, and multiple clock domains. Techniques to make failures reproducible [Heath 04][Sarangi 06][Silas 03] are often intrusive to system operation, and may not expose bugs.

2) System-level simulation: Most existing techniques require golden responses, *i.e.*, correct signal values for every clock cycle for the entire system (*i.e.*, the chip and all the peripheral devices on the board) to compare against the signal values produced by the chip being validated. System-level simulation is generally 7-8 orders of magnitude slower than actual silicon [Bentley 01][Nakamura 04] and in addition, expensive external logic analyzers are required to record all signals values that enter and exit the processor through external pins [Silas 03].

Due to these factors, a logic bug typically takes hours to days to be localized vs. an electrical bug that requires days to weeks and more expensive equipments [Josephson 01]. Hence, this report focuses on localization of electrical bugs.

#### **1.3 CONTRIBUTIONS**

The major contributions of this report are:

1) **Bug localization technique overcoming existing challenges**: This dissertation presents *IFRA* (*Instruction Footprint Recording and Analysis*), which is a new technique for localizing electrical bugs in processors without requiring system-level failure reproduction and system-level simulation. During normal operation of a processor in a post-silicon validation setup, special on-chip recorders collect information about flows of instructions through the processor and what the instructions did as they passed through various design blocks. Upon system failure, the recorded information is scanned out and analyzed offline using special self-consistency-based analysis techniques to localize hardware bugs. Evaluation of IFRA on an open-source microarchitectural simulator modeling Alpha 21264

[Digital 99] demonstrates high bug localization accuracy (96%) at low area overhead (1%).

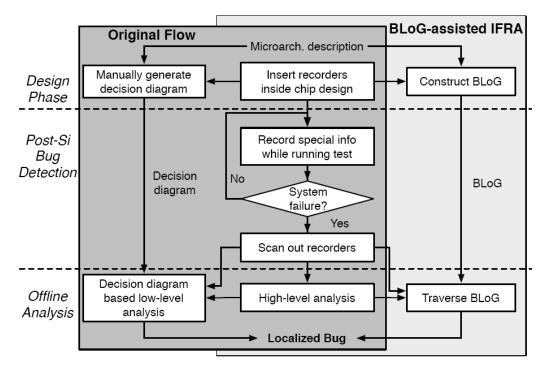

- 2) Framework for implementing IFRA on different microarchitectures: Applying IFRA to new microarchitectures can be challenging because it requires some degree of manual effort. This report presents *BLoG* (*Bug Localization Graph*), a new framework that enables systematic implementation of IFRA and automatic execution of IFRA for different microarchitectures.

- 3) BLoG-assisted IFRA for a commercial Intel processor: We use the BLoG framework to implement IFRA on an Intel® Core<sup>™</sup> i7 processor [Casazza 09] and demonstrate the effectiveness of BLoG-assisted IFRA using an industrial-grade microarchitectural simulator extensively used during product development. BLoG-assisted IFRA achieves high bug localization accuracy of over 90%.

### **1.4 OUTLINE**

Chapter 2 describes hardware support required for IFRA and various analysis techniques used to localize bugs from the recorded data. It also presents simulation results obtained from an open-source microarchitectural simulator modeling Alpha 21264. Chapter 3 presents the BLoG framework and evaluation results of BLoG-assisted IFRA for a commercial Intel processor, followed by conclusions in Chapter 4.

## CHAPTER 2. POST-SILICON BUG LOCALIZATION IN PROCESSORS USING IFRA

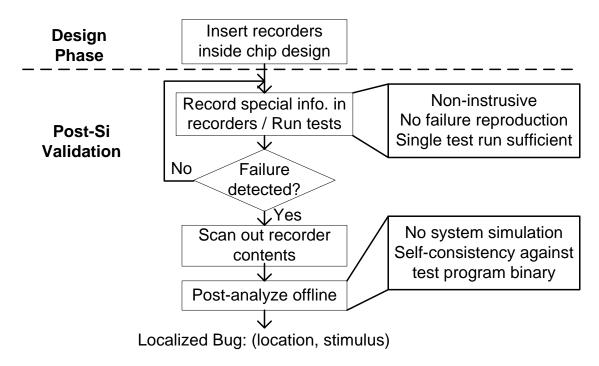

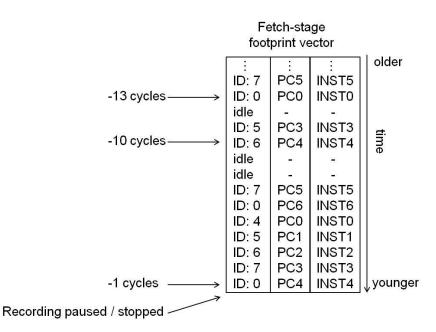

This chapter targets localization of electrical bugs in processors using a technique called *IFRA*, an acronym for Instruction Footprint Recording and Analysis. We did not investigate IFRA's applicability to logic bugs, because there is little consensus about models of logic bugs [ITRS 07]. Fig. 2.1 shows a post-silicon bug localization flow using IFRA. During chip design, a processor is augmented with low-cost hardware recorders for recording instruction footprints. *Instruction footprints* (or simply, *footprints*) are compact pieces of information describing the flows of instructions (*i.e.*, where each instruction was at various points in time), and what the instructions did as they passed through various design blocks of the processor. During post-silicon bug detection, instruction footprints are recorded in each recorder, concurrently with system operation, to capture the last few thousand cycles of history before a failure appears.

Fig. 2.1. Post-silicon bug localization flow using IFRA.

Upon detection of a system failure, the recorded footprints are scanned out through a Boundary-scan JTAG interface. IFRA uses special techniques (Sec.2.2) to ensure that a single test run is sufficient in capturing all the necessary information. Hence, there is no need to reproduce the failure for localization purposes.

Scanned-out footprints, together with the test program binary executed during postsilicon bug detection, are post-processed off-line using special analysis techniques (Sec. 2.3). These techniques identify both location (*e.g.*, the instruction queue control unit, scheduler, forwarding path, and decoder) and clock cycle in which an electrical bug had caused an error in a flip-flop in the design. The instruction sequence that exposes the bug (*i.e.*, the *bug exposing stimulus*) is then derived. The analysis techniques do not require any system-level simulation because they rely on *self-consistency-based checks* that inspect for the existence of contradictory events in scanned-out footprints with respect to the test program binary.

Once a bug is localized using IFRA, existing circuit-level debug techniques [Caty 05][Josephson 06] may be used to quickly identify root causes of bugs. Hence, IFRA can enable significant gains in productivity, cost, and time-to-market. One method of circuit-level debugging is to derive thousands of structural test patterns from the bug exposing stimulus and apply them to the microarchitectural blocks in close vicinity to the location at which IFRA identified the bug (the localized block), while sweeping over voltage, frequency and temperature ranges. Another method is to run the exposing stimulus while directing observation (*e.g.*, trace buffers [Abramovici 06]) and control mechanisms (*e.g.*, clock manipulation [Josephson 06]) to the localized block or its neighboring microarchitectural block(s).

Sec. 2.1 describes a processor model, which IFRA is going to target. Sec. 2.2 describes hardware support required for IFRA, while Sec. 2.3 describes post-analysis performed on the scanned-out footprint. Sec. 2.4 presents simulation results, followed by related work in Sec. 2.5, and conclusions in Sec. 2.6.

#### **2.1 TARGET PROCESSOR MODEL**

There are three features and four assumptions on the processor model that IFRA is targeting. The features demonstrate generality of IFRA, while the assumptions describe traits of our particular model that are shared with modern superscalar processors [Shen 05].

**Feature 1: Pipeline with out-of-order execution:** There are four in-order (fetch, decode, dispatch, commit) and two out-of-order pipeline stages (issue, execute). Instructions enter the centralized issue queue in-order (a process called dispatch), but exit the issue queue out-of-order (a process called issue). Instructions enter (during dispatch) and exit (during commit) the ROB (reorder buffer) in order. The maximum number of instructions-in-flight, *n*, equals the number of ROB entries in a superscalar processor. We are targeting out-of-order processors, but for simpler in-order processors (*e.g.*, ARMv6, Intel Atom, SUN Niagara cores), the entire IFRA-based analysis can be significantly simplified.

**Feature 2: Multiple clock domains:** For the execution stage, the granularity of individual clock domains can be as fine as to include a single type of functional units, but not finer. For example, if there are three ALUs and two load/store units, IFRA can support two separate domains with one containing all the ALUs and the other containing all the load/store units. For the rest of the pipeline stages, the granularity of individual clock domains can be as fine as a single pipeline stage, but not finer.

**Feature 3: Dynamic voltage and frequency scaling:** Individual clock domains can undergo independent dynamic voltage and frequency scaling.

**Assumption 1: Branch misprediction handling:** Mispredicted branch instructions are detected by branch units in the execution stage and the corresponding pipeline flushes (process of removing instructions in the middle of execution to enforce a change in control flow) are initiated only after the branch instruction exits the execution stage.

**Assumption 2: D-TLB miss handling:** D-TLB misses behave similar to branch mispredictions in that they both cause pipeline flushes. However, an instruction with a D-TLB miss causes a pipeline flush only when the instruction reaches the head of the ROB (*i.e.*, it is the instruction's turn to commit).

Assumption 3: External interrupts and I-TLB miss handling: Both external interrupts (an asynchronous signal indicating a need for a program flow change - e.g., process context switch) and I-TLB misses are associated with the instruction at the tail of the ROB at the time of occurrence. After the occurrence, the processor stops fetching new instructions and allows the instructions that are already in the pipeline to commit.

**Assumption 4: Fatal exception handling:** Once an instruction with a fatal exception reaches the head of the ROB, the processor is halted without any pipeline flushes.

**Assumption 5: Test program binary:** Binary is statically linked so their PCs (Program Counter) can be inferred after system failure. Otherwise, we would increase total storage from 60 Kbytes to 76 Kbytes to record instruction words in the recorders (more details in Sec. 2.2.1)

### 2.2 IFRA HARDWARE SUPPORT

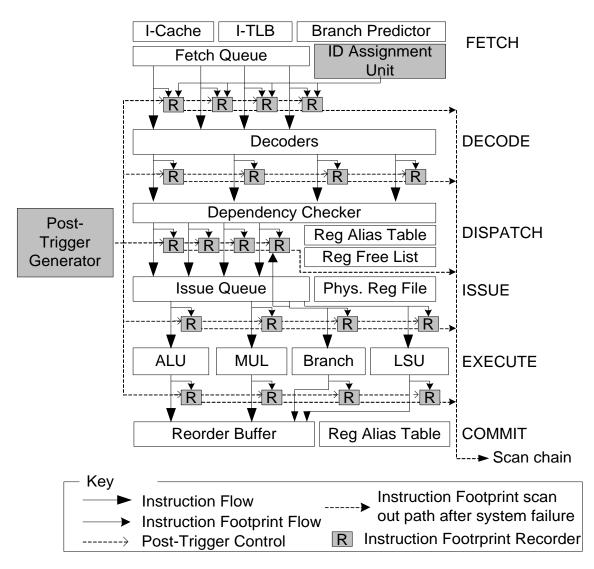

We use an Alpha 21264-like 4-way superscalar processor model [Digital 99] to explain the IFRA recording infrastructure. The shaded parts in Fig. 2.2 indicate the three hardware components of IFRA:

- A set of distributed instruction footprint recorders (denoted by 'R' in Fig. 2.2) with dedicated storage. Each recorder is associated with a pipeline stage, and collects instruction footprints corresponding to the associated stage.

- 2) An ID assignment unit for assigning and appending an ID to each instruction that enters the processor.

- 3) A post-trigger generator for pausing or stopping recording.

When an instruction, with an ID appended, flows through a pipeline stage, it generates an instruction footprint corresponding to that pipeline stage which is stored in the recorder associated with that pipeline stage. An instruction footprint consists of:

- 1) The ID corresponding to the instruction.

- 2) *Auxiliary information* corresponding to the pipeline stage that tells us what the instruction did in the microarchitectural blocks contained in that pipeline stage.

Even if a processor were bug-free, there may be bugs inside IFRA hardware. Electrical bugs affecting only IFRA hardware structures may result in two outcomes:

- 1) False post-trigger activation; or

- 2) Errors in the recorded data but not in the pipeline.

Because the recording operation and the post-trigger generation are performed by independent hardware, errors affecting only one of the two do not cause false positives (*i.e.*, a false indication of a bug in a bug-free processor). For the first case, the scanned-out footprints will indicate that the post-trigger was not supposed to activate. For the second case, since erroneous recorded data alone can never generate a post-trigger, the recorded data will be overwritten unnoticed.

Fig. 2.2. Superscalar processor augmented with recording infrastructure.

#### **2.2.1 INSTRUCTION FOOTPRINT RECORDER**

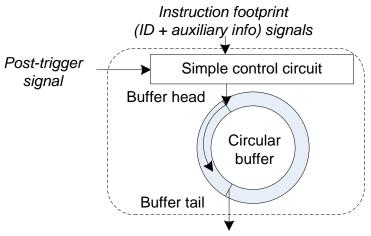

As shown in Fig. 2.3, each recorder consists of a circular buffer and simple control logic. Each pair of Instruction ID and auxiliary information enters and fills up the circular buffer during test run and is scanned out after a system failure. The control circuitry is responsible for four tasks:

- 1) Compacting idle cycles;

- 2) Controlling circular buffer operations;

- Starting/resuming and stopping/pausing recording according to the post-trigger signal;

- 4) Serializing buffer contents when they are scanned out.

Footprints scanned out after system failure

Fig. 2.3. Internal structure of a footprint recorder.

Table 2.1 shows the auxiliary information collected in each pipeline stage. Decoded bits corresponding to an instruction, collected at the decode stage, tell us which functional unit the instruction is going to use (2 bits), whether it uses a destination register (1 bit), and/or a second operand register (1 bit). The 2-bit and 3-bit residues are obtained by performing mod-3 and mod-7 operations on the original values, respectively. The commit-stage recorder, rather than having a circular buffer, has one register that records the ID of the youngest committed instruction along with any fatal exceptions it caused.

|                                                                                                            | Auxiliary information                          | Number               | Entries         |                 |  |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------|-----------------|-----------------|--|

| Pipeline stage                                                                                             | Description                                    | Bits<br>per<br>entry | of<br>recorders | per<br>Recorder |  |

| Fetch                                                                                                      | Program counter                                | 32                   | 4               | 1,024           |  |

| Decode                                                                                                     | Decoded bits                                   | 4                    | 4               | 1,024           |  |

| Dispatch                                                                                                   | 2-bit residue of register<br>name              | 6                    | 4               | 1,024           |  |

| Issue                                                                                                      | 3-bit residue of operands                      | 6                    | 4               | 1,024           |  |

| ALU, MUL                                                                                                   | 3-bit residue of result                        | 3                    | 4               | 1,024           |  |

| Branch                                                                                                     | None                                           | 0                    | 2               | 1,024           |  |

| LSU                                                                                                        | LSU 3-bit residue of result;<br>memory address |                      | 2               | 1,024           |  |

| Commit                                                                                                     | Fatal exceptions                               | 4                    | 1               | 1               |  |

| Total storage required for all recorders:<br>(Each entry has an additional 8-bit ID (Sec. 2.2.2))60 Kbytes |                                                |                      |                 |                 |  |

Table 2.1. Auxiliary information for Alpha microarchitecture.

Synthesis results (using Synopsys Design Compiler with a TSMC  $0.13\mu$  library) show that the area impact of the IFRA hardware infrastructure is 1% on the Illinois Verilog Model [Wang 04], assuming a 2MByte on-chip cache, which is typical for current desktop/server processors. This overhead is largely dominated by the circular buffers present in the recorders. Wires connecting the recorders (shown in Fig 2.2) operate at slow speed, and a large portion of this routing reuses existing on-chip scan chains that are present for manufacturing testing. If on-chip trace buffers [Abramovici 06] already exist for validation purposes, they can be reused to reduce the area impact. Alternatively, a part of data cache may also be used [Agarwal 86] to reduce the area impact of IFRA.

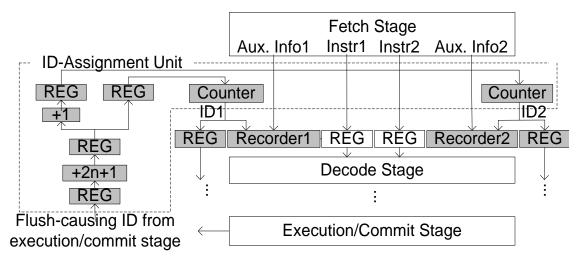

#### **2.2.2 ID-ASSIGNMENT UNIT**

There must be a method of identifying which set of the recorded data, stored across multiple recorders, belong to a particular instruction that was in-flight in the processor. Each footprint can be tagged with an identifier, or an ID, but the choice of the ID assignment scheme is important.

Many possible simplistic ID assignment schemes exist, each with their own limitations. For example, a scheme can assign consecutive numbers in a circular fashion to each incoming instruction. However, if IDs are too short (*e.g.*, 8-bit IDs if there can be only 256 instructions in a processor at any point in time), then complex recorders are required that are capable of removing footprints in the event of a pipeline flush. Having wider IDs will solve this problem, but will suffer from large storage requirement (*e.g.*, 40-bit ID will increase the storage requirement to 160Kbytes from 60Kbytes). Another option that does not require complex recorders would be to use global timestamps in addition to the short IDs, but this scheme also suffers from large storage requirements. The schemes that do not require complex recorders suffer even more in the presence of multiple clock domains with voltage and frequency scaling (DVFS).

Using PC values as IDs does not work for processors supporting out-of-order execution. Programs with loops may produce multiple instances of the same instruction with the same PC value. These multiple instances may execute out of program order.

Our special ID assignment scheme, described below, uses  $log_24n$  bits, where *n* is the maximum number of instructions in a processor at any one time (*e.g.*, *n* = 64 for Alpha 21264). The first two rules assign consecutive numbers in a circular fashion to incoming instructions while the third rule allows the scheme to work (proof in Appendix A) under all the aforementioned circumstances: *i.e.*, for processors supporting out-of-order execution, pipeline flushes, multiple clock domains and DVFS. Instruction IDs are assigned to individual instructions as they exit the fetch stage and enter the decode stage

(Fig. 2.4). Since multiple instructions may exit the fetch stage in parallel at any given clock cycle, multiple IDs are assigned in parallel.

Fig. 2.4. ID-assignment unit for a 2-way processor.

#### Instruction ID Assignment Scheme used by IFRA:

<u>Rule 1</u>: The first *p* instructions that exit the fetch stage in parallel are assigned IDs, 0, 1, 2, ..., p-1.

<u>Rule 2</u>: Let ID X be the last ID that was assigned. If there are q instructions that exit the fetch stage in the current cycle in parallel, then q IDs,  $X+1 \pmod{4n}$ ,  $X+2 \pmod{4n}$ , ...,  $X+q \pmod{4n}$  are assigned to the q instructions.

<u>Rule 3</u>: If an instruction with ID *Y* causes a pipeline flush, then the ID *X* in Rule 2 is overwritten with the value of  $Y+2n \pmod{4n}$ . As a result, ID of  $Y+2n+1 \pmod{4n}$  is assigned to the first instruction that is fetched after the flush.

There exists sufficient time between instantiations of Rules 3 and 2 to overwrite the ID X with  $Y+2n \pmod{4n}$  before newly fetched instructions arrive at the ID assignment unit. This is because it takes several cycles (*e.g.*, Alpha 21264 has 3 pipeline stages within the fetch stage) for the instructions to propagate from the beginning to the end of the fetch stage.

#### 2.2.3 POST-TRIGGER GENERATOR

Suppose that a test program has been executing for billions of cycles and an electrical bug is exercised after 5 billion cycles from start. Moreover, suppose that the electrical bug causes a system crash after another 1 billion cycles. With limited storage, we are only interested in capturing the information around the time when the electrical bug is exercised. Hence, five billions of cycles worth of information before the bug occurrence may not be necessary. On the other hand, if we stop recording only after the system crashes, all the useful recorded information will be overwritten. Thus, we must incorporate mechanisms, referred to as *post-triggers*, for reducing *error detection latency*, the length of time between the appearance of an error caused by a bug and system failure.

Post-triggers targeting five different failure scenarios are listed in Table 2.2. A *hard post-trigger* fires when there is an evident sign of failure, and causes the processor operation to terminate. Classical hardware error detection techniques such as parity bits for arrays (*e.g.*, register file, ROB, register free list, and various queues) and residue codes for arithmetic units in ALUs and address calculators exist in several commercial processors [Ando 03][Sanda 08]. Fatal exceptions, such as unimplemented instruction exceptions, arithmetic exceptions and alignment exceptions are already present in most processors.

However, hard post-triggers mechanisms alone are not sufficient, *e.g.*, two tricky scenarios described in the last 2 rows of Table 2.2. These two failure scenarios may be detected several millions of cycles after an error occurs, causing useful recorded information to be overwritten even with the existing error detection mechanisms. Hence, we introduce the notion of *soft post-triggers*. A soft post-trigger fires when there is an early symptom of a possible failure. It causes the recording in all recorders to pause, but allows the processor to keep running. If a hard post-trigger for the failure corresponding to the symptom occurs within a pre-specified amount of time, the processor stops. If a hard post-trigger does not fire within the specified time, the recording resumes assuming that the symptom was false.

For deadlocks, a soft post trigger event fires when no instruction retires within the time required to perform two memory loads. The corresponding hard post trigger event is two additional seconds of no retirement [Mahmood 88].

Segmentation faults (or segfaults) require OS handling and, hence, may take several millions of cycles to resolve. Null-pointer dereferences are detected by adding simple hardware to detect whether the memory address equals zero in the Load/Store unit. For other illegal memory accesses, a TLB-miss signal is used as a soft post-trigger. If a segfault is not declared by the OS while servicing the TLB-miss, the recording is resumed on TLB-refill. On the other hand, if a segfault is returned, then a hard post-trigger is activated. The pause in the recording may create a period of time that acts as a blind spot during post-silicon validation. In order to cover such blind spots, a separate set of functional tests specifically targeting TLB servicing must be designed to identify bugs that may appear during TLB-misses. While running such tests, soft-triggers targeting segfault must be disabled so that recorders do not pause during the TLB servicing.

Silent data corruption and live-locks are not covered by the current set of post-triggers. Use of a wider variety of post-triggers based on hardware assertions [Abramovici 06][Bayazit 05], software assertions, and symptoms [Wang 04] is a topic of future research.

| Failure Scenario | Post-triggers                                                    |                                             |  |  |  |

|------------------|------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Failure Scenario | Soft                                                             | Hard                                        |  |  |  |

| Array error      | -                                                                | Parity check                                |  |  |  |

| Arithmetic error | -                                                                | Residue check                               |  |  |  |

| Fatal exceptions | -                                                                | In-built exceptions                         |  |  |  |

| Deadlock         | Short (2 mem loads)<br>instruction retirement gap                | Long (2 secs) instruction<br>retirement gap |  |  |  |

| Segfault         | TLB-miss + TLB-refill<br>(for both data and<br>instruction TLBs) | Segfault from OS,<br>Address equals 0       |  |  |  |

Table 2.2. Failure scenarios and post-triggers.

### **2.3 POST-ANALYSIS TECHNIQUES**

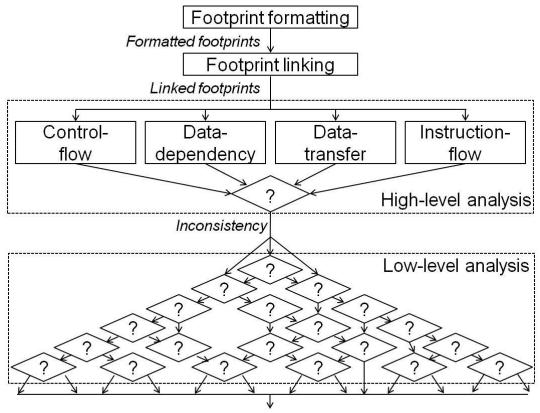

Once recorder contents are scanned out and formatted (Sec. 2.3.1) appropriately, footprints belonging to the same instruction (but in multiple recorders) are identified and linked together using a technique called *footprint linking* (Sec. 2.3.2) as shown in Fig. 2.5. The linked footprints are also mapped to the corresponding instruction in the test program binary using the PC values stored in the fetch-stage recorder. After which, two sets of self-consistency-based checks are run, inspecting for the existence of contradictory events in linked footprints with respect to the test program binary. A set of microarchitecture-independent checks, referred to as high-level analysis (Sec. 2.3.3), finds the first sign of an *inconsistency* in program execution. The information on the discovered inconsistency is passed along to the next step in the form of a *<location*, *footprint> pair* (Sec. 2.3.2.2). Starting from the inconsistency, the next step runs a set of microarchitecture-dependent checks, referred to as low-level analysis (Sec. 2.3.4), identifying a set *bug candidates*, which are also in the form of <location, footprint> pairs. From the bug candidates, corresponding exposing stimuli are derived (Sec. 2.3.5). The low-level analysis asks a series of microarchitecture-specific questions according to a manually-generated decision diagram. A technique for minimizing the manual effort is presented later in Chapter 3.

The post-analysis techniques rely on the concept of self-consistency. While such checks are extensively used in fault-tolerant computing for error detection [Austin 99][Lu 82][Oh 02][Siewiorek 98], we use them for bug localization. Such application is possible because, unlike fault-tolerant computing, the checks are performed off-line enabling deeper analysis for localization purposes.

Bug candidates

Fig. 2.5. Post-analysis summary.

#### **2.3.1 FORMATTING SCANNED-OUT FOOTPRINTS**

After scanning out footprints from individual recorders, the following six steps format the set of footprints before linking:

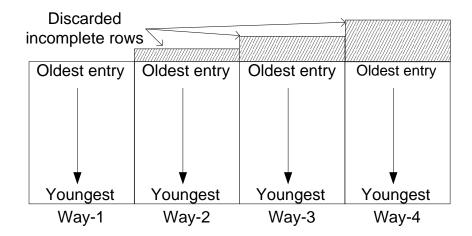

- 1) **Unwrap circular buffers:** The footprints scanned out from each circular buffer are unwrapped so that the youngest entry appears at the bottom and the oldest entry appears at the top (Fig. 2.6).

- Expand idle cycles: While recording footprints, consecutive idle cycles are compacted to occupy a single entry. The compacted entries are expanded back so that each entry corresponds to a clock cycle.

- 3) Align circular buffers: The unwrapped circular buffers associated with each pipeline stage are collected and juxtaposed so that the youngest entries are aligned (Fig. 2.6). Due to the 2<sup>nd</sup> feature of our processor model (Sec. 2.1), each row in the juxtaposed buffers corresponds to the same clock cycle.

- 4) **Discard incomplete rows:** For a given pipeline stage, some recorders record longer history than others because they encounter more idle cycles. For simplicity of analysis, incomplete rows are discarded (Fig. 2.6). The resulting matrix of footprints is referred to as *footprint matrix*.

- 5) **Convert to footprint vector:** Footprint matrices associated with in-order pipeline stages are converted into *footprint vectors*, where (i,j)<sup>th</sup> entry of the matrix corresponds to (wi+j)<sup>th</sup> entry of the vector, for a *w*-way stage. Footprint matrices associated with out-of-order pipeline stages are retained.

- 6) Augment fetch-stage footprint vector: Footprint vector associated with the fetch-stage is augmented with an additional auxiliary information field to contain instruction words (Fig. 2.7). Since PC is stored in the fetch-stage recorder (Table 2.1), instruction word corresponding to each PC can be obtained from the test program binary.

Fig. 2.6. Aligning four unwrapped circular buffers for a 4-way pipeline stage.

| Test pr<br>bin | ogram<br>ary |     | Fetch-s | stage<br>t vector |                                       |     |       |     |       |

|----------------|--------------|-----|---------|-------------------|---------------------------------------|-----|-------|-----|-------|

|                |              | łΓ  | 1       |                   |                                       |     |       |     | :     |

| i i            |              | Ì   | ID: 7   | PC5               |                                       |     | ID: 7 | PC5 | INST5 |

| PC0            | INST0        | ł   | ID: 0   | PC0               |                                       |     | ID: 0 | PC0 | INST0 |

| PC1            | INST1        | !   | ID: 5   | PC3               |                                       |     | ID: 5 | PC3 | INST3 |

| PC2            | INST2        | i l | ID: 6   | PC4               |                                       | Ν   | ID: 6 | PC4 | INST4 |

| PC3            | INST3        | 1   | ID: 7   | PC5               |                                       | _ > | ID: 7 | PC5 | INST5 |

| PC4            | INST4        | i   | ID: 0   | PC6               | i i i i i i i i i i i i i i i i i i i | ٦/  | ID: 0 | PC6 | INST6 |

| PC5            | INST5        | 1   | ID: 4   | PC0               |                                       | V   | ID: 4 | PC0 | INST0 |

| PC6            | INST6        | i   | ID: 5   | PC1               |                                       |     | ID: 5 | PC1 | INST1 |

|                | :            |     | ID: 6   | PC2               |                                       |     | ID: 6 | PC2 | INST2 |

|                | ~~           | !   | ID: 7   | PC3               |                                       |     | ID: 7 | PC3 | INST3 |

|                |              | i   | ID: 0   | PC4               |                                       |     | ID: 0 | PC4 | INST4 |

Fig. 2.7. Fetch-stage footprint vector augmented with instruction words.

#### **2.3.2 FOOTPRINT LINKING**

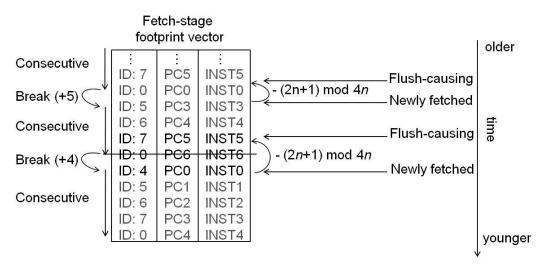

Fig. 2.8 shows part of a test program binary and the contents of three (out of many) recorders, right after they are scanned out. As explained in Sec. 2.2.2, since we use short instruction IDs (8-bits for Alpha 21264-like processor), we end up having multiple footprints having the same ID in the same recorder and /or multiple recorders. For example, in Fig. 2.8, ID 0 appears in three entries of the fetch-stage footprint vector, in two entries of the issue-stage footprint matrix (with a single column), and in three entries of the ALU footprint matrix (with a single column).

Footprint linking analyzes ID sequence to identify which of these ID 0s belongs to the same instruction. The ID assignment scheme presented in Sec. 2.2.2 enforces the following properties on the ID sequence (proof in Appendix A):

- Property 1) All flushed instructions are uniquely identified by using Rule 3 of the ID assignment scheme;

- Property 2) If instruction A was fetched before instruction B, and they both have the same ID, then A will always exit any pipeline stage (and leave its footprint in the corresponding recorder) before B does for that same pipeline stage.

In Fig. 2.8, using the first property, all flushed instructions with ID 0s are identified and discarded. Fig. 2.9 shows how the identification is done for the fetch-stage footprint vector. The example corresponds to a processor with n, the maximum number of in-flight instructions, equal to 2. The fetch stage processes instructions in program order. The first step is to identify breaks in consecutive IDs, *e.g.*, there is a break between the second youngest ID 0 and ID 4. The gap immediately indicates that the ID 4 belongs to a newly-fetched instruction after a pipeline flush. Subtracting 2n + 1 from ID 4 identifies the ID of a flush-causing instruction. All IDs between the flush-causing (ID 7) and the newly-fetched (ID 4) correspond to flushed instructions. Similar analysis is done for all other breaks in the consecutive assignment to identify IDs corresponding to flush-causing, flushed, committed and uncommitted instructions. For pipeline stages that process

instructions out of program order (e.g., issue- and execution-stages), identification of flushed instructions is more complex (full details in the Appendix A).

After the flushed instructions are identified and discarded, using the second property, the youngest instances of ID 0 across all vectors/matrices are linked together, followed by linking of the second youngest instances of ID 0, and so on.

|     | Fetch-stage<br>footprint vector |     |       |   |        | -stage<br>nt matrix |        | LU<br>nt matrix |              |

|-----|---------------------------------|-----|-------|---|--------|---------------------|--------|-----------------|--------------|

| 3   | :                               | :   | :     |   | :      | :                   |        |                 | older        |

|     | ID: 7                           | PC5 | INST5 |   | 7ID: 0 | AUX0                | :      |                 |              |

|     | ID: 0                           | PC0 | INST0 | K | ID: 7  | AUX1                | HD: 0  | AUX20           |              |

|     | ID: 5                           | PC3 | INST3 |   | ID: 6  | AUX2                | ID: 7  | AUX21           |              |

|     | ID: 6                           | PC4 | INST4 |   | ID: 5  | AUX3                | ID: 5  | AUX22           |              |

|     | ID: 7                           | PC5 | INST5 |   | ID: 0  | AUX4                | ID: 6  | AUX23           | time         |

| 100 | ID: 0                           | PC6 | INST6 |   | ID: 7  | AUX5                | ID: 7  | AUX24           | Ō            |

|     | ID: 4                           | PC0 | INST0 |   | ID: 5  | AUX6                | ID: 5  | AUX25           |              |

|     | ID: 5                           | PC1 | INST1 |   | ID: 4  | AUX7                | ID: 4  | AUX26           |              |

|     | ID: 6                           | PC2 | INST2 |   | ID: 6  | AUX8                | ID: 6  | AUX27           |              |

|     | ID: 7                           | PC3 | INST3 |   | JD: 0  | AUX9                | ID: 7  | AUX28           | younger      |

|     | ID: 0                           | PC4 | INST4 | K | ID: 7  | AUX10               | ≥ID: 0 | AUX29           | $\downarrow$ |

Fig. 2.8. Footprint linking, with a max number of 2 instructions in flight.

Fig. 2.9. Flushed / flush-causing instructions in fetch stage footprint vector.

Linked footprints provide the following information for each instruction that was in-flight in the processor:

- 1) Whether it was committed or uncommitted;

- 2) Whether it was flush-causing, flushed or neither;

- The cycle when the instruction went through a particular pipeline stage relative to the cycle when the recording was stopped / paused for that stage;

- 4) The operation the instruction was performing at a particular pipeline stage.

#### **2.3.2.1 Footprint Pointer**

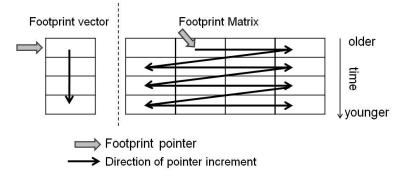

We define *footprint pointer*. A footprint pointer for a footprint vector/matrix points to a vector/matrix entry that contains a single footprint. When incrementing a pointer for a footprint matrix, the pointer accesses the matrix in row-major order (*i.e.*, left to right in a row and then from oldest to youngest row) as shown in Fig. 2.10.

Fig. 2.10. Footprint pointer and direction of pointer increment.

A footprint pointer indicates a cycle within a pipeline stage, relative to the cycle when the post-trigger was recieved. For example, consider the fetch-stage footprint vector shown in Fig. 2.11. Compacted consecutive idle cycles are expanded back, as described in Sec. 2.3.1 and the youngest footprint is the one recorded just before receiving a post-trigger. Since each entry corresponds to a cycle within a pipeline stage, the difference from the tail pointer indicates the relative cycle from the cycle when the recording was stopped for that pipeline stage, as shown in the figure. If a single clock domain is used for the entire processor, as opposed to having a separate clock domain for each pipeline stages, then the footprint pointer would indicate a global cycle within the processor instead.

Fig. 2.11. Footprints indicating cycles within a pipeline stage.

#### 2.3.2.2 <Location, Footprint> Pair

We define <location, footprint> pair. The location element of the pair indicates a design block containing an erroneous flip-flop affected by an electrical bug. The footprint element of the pair is a footprint pointer that indicates a cycle within a pipeline stage when the erroneous behavior occurred.

#### 2.3.2.3 Follow\_link() Operator

We define a new operator, *follow\_link()*. It takes three inputs – source footprint pointer, source footprint vector, destination footprint vector – and returns a destination footprint pointer. While the source pointer points into the source footprint vector entry that contains a footprint belonging to a particular instruction, the operator returns a pointer into the destination footprint vector entry that contains the footprint belonging to the same instruction. A similar operator can be defined for footprint matrices, and we will be overloading the operator to include all combinations of footprint vector and matrices as source and destination.

#### 2.3.2.4 Footprint Pointer Comparison Operator

We define a comparison operator for two footprint pointers, *P1* and *P2*, pointing at two different footprint vector/matrices. Denote the footprint vector/matrix pointed by *P1* and *P2* as *F1* and *F2*. The comparison *P1* > *P2* then becomes *follow\_link (P1, F1,* fetch-stage) > *follow\_link(P2, F2,* fetch-stage). The > operator can be replaced with any other relational operators (=,  $\neq$ , <,  $\geq$ ,  $\leq$ ,). For two footprint pointers pointing at the same footprint vector, perform numerical comparison of the pointers, and for the pointers pointing at the same matrix, perform numerical comparison of the row numbers.

## **2.3.3 HIGH-LEVEL ANALYSIS<sup>1</sup>**

We have four high-level analysis techniques:

- 1) Data-dependency analysis;

- 2) Control-flow analysis;

- 3) Data-transfer analysis;

- 4) Instruction-flow analysis.

Each analysis technique is applied separately, starting from the oldest entry in the footprint vectors/matrices until any inconsistency is sighted. Each inconsistency is represented as a <location, footprint> pair (Sec. 2.3.2.2), where the location element of the pair dictates the entry point into the decision diagram used for the low-level analysis.

If only one of the analysis techniques identifies an inconsistency, then the corresponding entry point into the decision diagram is taken. If none of them discovers an inconsistency, then there is a default entry point into the decision diagram. If multiple of them identify inconsistencies, then there are two options:

- 1) Perform low-level analysis from each entry point corresponding to each inconsistency separately and then combine the results.

- 2) Since we are interested in the inconsistency that is closest to the electrical bug manifestation in terms of time, the reported inconsistencies are compared (as defined in Sec.2.3.2.4) to see which one occurred the earliest. The high-level analysis technique with the earliest occurring inconsistency then dictates the entry point into the decision diagram for the low-level analysis.

Our results are reported using the second option. Investigation of the first option is a topic of future research.

<sup>&</sup>lt;sup>1</sup> The high-level analysis has been updated from the version shown in [Park 09] so that the result of the high-level analysis can be directly used by the BLoG framework presented in Chapter 3.

#### 2.3.3.1 Data-dependency Analysis

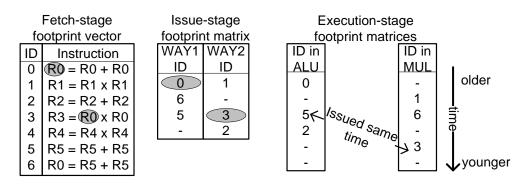

This analysis technique verifies whether the instruction data dependency order [Shen 05] is preserved; *i.e.*, the analysis verifies that every committed instruction A is issued only after all instructions that would produce A's operands finish execution. Let B be the producer instruction without loss of generality. Use the fetch-stage-footprint-vector to identify vector entries corresponding to A and B and denote them with two pointers Pfa and Pfb. Then perform follow\_link (Pfa, fetch-stage, issue-stage) to obtain Pia to an issue-stage-footprint-matrix entry. Create new pointers, Picl...PicN, where each pointer points to each of the committed footprints that are on the same row as the footprint pointed by Pia. N is the number of committed footprints on the same row, including the one pointed by *Pia*. Perform *follow\_link* ("source pointer", issue-stage, execution-stage) by replacing "source pointer" with each of the Pic1...PicN, to obtain Pe1 ... PeN. For each of *Peal* ... *PeaN*, move the pointer by number of rows equal to the latency associated with the execution unit. For example, for an execution-stage footprint matrix corresponding to an ALU with 3-cycle latency, the pointer will be moved up by 3 rows. Then perform follow\_link (Pfb, fetch-stage, execution-stage) to obtain Peb. If Peb is in the row below any of the *Peal* ... *PeaN*, then there is a data dependency violation. A failed check returns <scheduler's issue-ready signal, *Pia*> as the <location, footprint> pair.

As an example, consider Fig. 2.12. Since instruction with ID 0 shown in the fetch-stage footprint vector produces a value on R0, while the instruction with ID 3 consumes a value from R0, data dependency exists between those two instructions. Instruction with ID 0 enters the ALU while the instruction with ID 3 enters the multiplier (shown in the execution-stage footprint matrices with single column each). Assume that the two functional units are in different clock domains, and also assume that the ALU has a latency of 3 cycles. Since the two dependent instructions are in different clock domains with a possibility of dynamic frequency scaling, it is not possible to directly check their relative timing. However, we know that the all the issue-stage recorders must be in a

single clock domain (feature 2 of Sec. 2.1), and thus know that the instructions with ID 3 and ID 5 must be issued at the same time (shown in the issue-stage footprint matrix). In this case, there is only two cycles difference between ID 3 and ID 0, which is shorter than the 3-cycle latency of the ALU. This implies the consumer instruction with ID 3 was issued prematurely, before the producer instruction with ID 0 has completed.

Fig. 2.12. Data-dependency analysis example.

#### 2.3.3.2 Control-flow Analysis

In the program control flow analysis, four types of illegal transitions are searched in the PC sequence of committed instructions in the fetch-stage footprint vector, starting from the oldest PC:

- The PC does not increment by +4 except in the presence of a control flow transition instruction (branch or jump);

- 2) The PC increments by +4 in the presence of unconditional transition instruction;

- The PC neither increments by +4 nor jump to the correct target specified as the immediate in the presence of direct transition instruction (with target address not dependent on a register value);

- 4) The PC does not jump to an address that is part of the executable address space (determined from the program binary) in the presence of register-indirect transition instructions (with target address that depends on a register value).

With a violation in control flow from instruction A to instruction B, the analysis returns <Program counter register of branch unit, pointer to A's fetch-stage footprint vector entry> as the <location, footprint> pair.

#### 2.3.3.3 Data-transfer Analysis

This technique verifies that a value loaded from a memory address matches with the value stored at that address. The check is performed on the load-store sequence obtained from load-store unit footprint matrix. The checks below return six types of inconsistencies and are performed upon each value stored to an address *a*, denoted w[a], and the subsequent (without an intervening store to *a*) values loaded from *a* denoted  $r[a](1) \dots r[a](n)$ .

A violation in Data-transfer analysis returns at least one and up to five of the following <location, footprint> pairs:

- Pair 1) <Address output of store address queue in load-store unit, pointer to *w*[*a*] in load-store unit footprint matrix>;

- Pair 2) <Address output of load queue in load-store unit, pointer to *r*[*a*](*k*) in loadstore unit footprint matrix>, where *k* is determined during the checks;

- Pair 3) <Data output of store data queue in load-store unit, pointer to *w*[*a*] in load-store unit footprint matrix>;

- Pair 4) <Load data output of load-store unit, pointer to r[a](k) in load-store unit footprint matrix>, where k is determined during the checks;

- Pair 5) <Memory, pointer to *w*[*a*] in load-store unit footprint matrix>;

- Pair 6) <Memory, pointer to r[a](k) in load-store unit footprint matrix>, where k is determined during the checks.

There are three checks performed by the data-transfer analysis:

If for all *i*, *j*, *r*[*a*](*i*) = *r*[*a*](*j*) (*i.e.*, all loads were consistent) and for all *i*, *w*[*a*] ≠ *r*[*a*](*i*), and *n* > 1 then the multiple consistent loads suggest that the store address was incorrect. Return pair 1 listed above. In addition, there is possibility that the memory write/read was incorrect. Since we are only concentrating on processor bugs, this inconsistency is not passed onto low-level analysis, but is appended on

to the list of candidate location-footprint pairs returned by low-level analysis. The inconsistency location-footprint pair is the pair 5 listed above.

- 2) If w[a] ≠ r[a](i), and n = 1 then since there is only one load, a bug in the load cannot be ruled out. Return pair 1 and 5 as was done in the previous check, along with 2, 4, and 6, where k = 1.

- 3) If there exists *i*, *j*, such that *r*[a](*i*) ≠ *r*[a](*j*) (*i.e.*, not all loads are consistent) then for each load *r*[a](*k*) ≠ *w*[a], pair 2, 4 and 6.

#### 2.3.3.4 Instruction-flow Analysis

This analysis checks whether instructions are decoded correctly, and whether they pass through the correct sequence of modules without disappearing or being modified erroneously in the middle.

The first consistency check is to verify, using the decode-stage bits, that only the recorder associated with the correct functional unit had recorded the instruction (*e.g.*, an ADD instruction does not go into a multiplier unit). A failed check returns the footprint of the incorrectly executed instruction in the execute-stage footprint matrix as the inconsistent footprint.

The next three checks ensure that footprints contained in earlier pipeline stages should be a superset of footprints (both committed and uncommitted) contained in later pipeline stages. For example, a decode-stage footprint vector cannot contain a footprint that is not present in fetch-stage footprint vector. Due to finite-sized buffers, we do not perform this check for all footprints. These checks impose an additional requirement of post-trigger routing: later pipeline stages must be stopped before or at the same time as earlier pipeline stages. Even if pipeline stages are not in the same clock domain, this can be done by stopping each stage from commit to fetch in sequence.

Consistency among footprint vectors: Create pointers P1, P2, and P3 to the youngest footprints of the fetch, decode, and dispatch footprint vectors. If P1 points to an uncommitted footprint with ID X, verify that if P2 does not point to X, then P3 does not either. A failure returns an erroneous flush inconsistency whose inconsistent footprint is the next older flush-causing footprint in the dispatch footprint vector. If P1 points to a committed footprint X, verify that both P2 and P3 point to X. A failure returns an inconsistency whose inconsistent footprint is X's footprint in the footprint vector associated with the pipeline stage before the stage which was missing X's footprint. Continue this check by incrementing the pointers that point to X to the next older entries of the respective footprint vectors. If a pointer cannot be incremented, stop. Consistency among footprint matrices: Given the issue-stage matrix and execute-stage matrix, we use the fact that issue order and execute order for a given functional unit are the same. Each functional unit is associated with a column in the issue and fetch stage footprint matrices. The prior check is performed between the two columns associated with each functional unit.

Consistency along the vector-matrix boundary (dispatch-stage vector and issue-stage matrix). Algorithms similar to that of Algorithm A in Appendix A are used to perform the following checks:

For each committed instruction in the issue-stage matrix, the algorithm checks that it appears in the dispatch-stage footprint vector as well. A failure returns a missing footprint inconsistency whose inconsistent footprint is X's footprint in the issue-stage footprint matrix.

When performing Step 6 of Algorithm A.3 in Appendix A (identifying uncommitted instructions in the footprint matrix), check that the uncommitted instructions have a one-to-one mapping to uncommitted instructions in the dispatch-stage footprint vector. More than one uncommitted footprint indicates a duplicated uncommitted footprint in the matrix or a missing flush-causing footprint in the matrix. A failure returns an erroneous flush inconsistency whose inconsistent footprint is the footprint of the flush-causing instruction in the dispatch-stage footprint matrix.

# **2.3.4** LOW-LEVEL ANALYSIS<sup>2</sup>

Given the inconsistency, in the form of a <location, footprint> pair, returned from the high-level analysis, the low-level analysis asks a series of microarchitecture-specific questions according to a manually-generated decision diagram (an example of which is shown in Appendix B). The location-element of the inconsistency decides the entry point into the decision diagram. While going through the decision diagram, the location and footprint elements are both updated to find the <location, footprint> pairs associated with the final bug candidates. The location element of a bug candidate indicates a possible design block containing the flip-flop that was first affected by an electrical bug, while the footprint element indicates the cycle in which the event took place.

## **2.3.5 BUG-EXPOSING STIMULUS**

Bug-exposing stimuli are derived from footprint elements of bug candidates. Denote the footprint pointer of a bug candidate as *Pbug* and the footprint vector/matrix pointed by *Pbug* as *Vbug*. Performing *follow\_link (Pbug, Vbug,* fetch-stage) returns a pointer partitioning the fetch-stage footprint vector into two parts. Older footprints correspond to the bug exposing stimulus, which is a trace of instructions leading up to the cycle in which the bug first caused an error in a flip-flop. Younger footprints correspond to trace of instructions responsible for propagating the error to an observable output.

<sup>&</sup>lt;sup>2</sup> We only briefly mention the low-level analysis here, because Chapter 3 describes a framework for systematically constructing a low-level analysis decision diagram and a method for traversing it.

## **2.4 RESULTS**

We evaluated IFRA by injecting errors into a microarchitectural simulator [Austin 02] augmented with IFRA. We used an Alpha 21264 configuration (4-way pipeline, 64 maximum instructions in-flight, 2 ALUs, 2 multipliers, 2 load/store units), which gave 200 different locations (excluding array structures and arithmetic units since errors inside those structures are immediately detected and localized using parity and residue codes, as discussed in Sec. 2.2.3). Each location has an average size equivalent of 10K 2-input NAND gates. Seven benchmarks from the SPECint2000 benchmark suite (bzip2, gcc, gap, gzip, mcf, parser, vortex) were chosen as validation test programs as they represent different types of workloads. Each recorder was sized to have 1,024 entries.

All bugs were modeled as single bit-flips at flip-flops to target hard-to-repeat electrical bugs. This is an effective model because most electrical bugs eventually manifest themselves as incorrect values arriving at flip-fops for certain input combinations and operating conditions [McLaughlin 09].

Errors were injected in one of 1,191 flip-flops (Table 2.3). No errors were injected in structures protected with built-in parities/residues for error detection. Errors were injected in input / output registers and various control registers controlling the array structures. Pipeline registers in Table 2.3 include decoded opcode, register specifiers, immediate data, addresses to arrays, etc. Valid bits indicate whether a given instruction is valid or not in a pipeline register.

| Description                            | Number of bits |

|----------------------------------------|----------------|

| PC, next PC                            | 128            |

| Memory Address used by Load/Store      | 128            |

| Input/Output latch of Array Structures | 82             |

| Pointers to Array structures           | 23             |

| Control states of Array Structures     | 4              |

| Pipeline Registers                     | 800            |

| Valid Bits                             | 26             |

Table 2.3. Error injection bits.

Upon error injection, the following scenarios are possible:

Case 1) The error is masked and causes no system-level effect [Wang 04].

- Case 2) The error is silent in that it does not cause any post-trigger mechanism to trigger, but the program output is incorrect [Wang 04].

- Case 3) Failure manifestation with short error detection latency, in which case the recorders successfully capture the history from error to failure manifestation (including situations where recording is paused upon activation of soft post-triggers).

- Case 4) Failure manifestation with long error latency, where 1024-entry recorders fail to capture the history from error to failure (including soft triggers).

Cases 1 and 2 are related to coverage of validation test programs and post-triggers, and are not the focus of this paper. Any error injection runs which does not result in the activation of any post-trigger within 100,000 cycles from the point of error injection was repeated with a new error injection run.

When case 3 occurs, IFRA-based post-analysis is performed to obtain a set of bug candidates in the form of <location, footprint> pairs. Each pair indicates a design block – which contains the flip-flop that is thought to be flipped in value – together with a cycle in which the bit-flip is thought to have occurred, relative to the cycle in which the system failure occurred.

Out of 100,000 error injection runs, 800 of them resulted in Cases 3 and 4. Table 2.4 presents results from these two cases. The "*exactly localized*" category represents the cases in which IFRA returned a single and correct <location, footprint> pair. The "*multiple candidates*" category represents the cases in which IFRA returned multiple bug candidates and at least one pair was fully correct in both location and in cycle. The "*completely missed*" category represents the cases where none of the returned pairs were correct. In addition, we pessimistically report all errors that resulted in Case 4 as "completely missed."

All error injections were performed after a million cycles from the beginning of the program in order to demonstrate that there is no need to keep track of all the footprints before the appearance of an error. It is clear from Table 2.4 that a large percentage of bugs were uniquely located to correct <location, footprint> pair, while very few bugs were completely missed, demonstrating the effectiveness of IFRA.

For "multiple candidates" cases, Table 2.4 also reports statistics on the number of possible candidates out of a total of 200,000 possible candidate <location, footprint> pairs. When IFRA identified multiple candidates, on average, it correctly dismissed 99.8% of the possible bug locations.

| Result category                              | Percentage                                    |

|----------------------------------------------|-----------------------------------------------|

| Exactly Localized                            | 75%                                           |

| Correctly Localized with multiple candidates | 21%<br>min. 2, avg. 6, and max. 34 candidates |

| Completely Missed                            | 4%                                            |

Table 2.4. IFRA bug localization summary.

## **2.5 RELATED WORK**

Related work on post-silicon validation can be broadly classified into the following categories: formal methods [De Paula 08], embedded trace buffers for hardware debugging [Abramovici 06], on-chip program and data tracing [MacNamee 00], clock manipulation [Josephson 06], scan dump [Caty 05], check-pointing with deterministic replay [Silas 03][Sarangi 06], and on-line assertion checking [Abramovici 06][Bayazit 05][Chen 08]. Table 2.5 provides a qualitative comparison of IFRA versus existing techniques.

Most of the techniques require failure reproduction and system-level simulation. If easy failure reproduction support is present, it will also help IFRA by allowing recorders to record unlimited lengths of history through repeated sampled recording and dumping.

On-chip storage of program and data traces [MacNamee 00], commonly used in embedded processors (e.g. ARM, Motorola's MPC, Infineon's Tricore), have some similarity with IFRA in that they also store program flow of the executed software. If one can assume perfect hardware, capturing the signals at the asynchronous interfaces is sufficient to reconstruct all the internal signals using simulation [Xu 03]. However, such information is only valid before an error occurs, and no reconstruction is possible beyond the error. Since bug localization requires information from error to failure, the application of the technique to hardware debugging is limited.

On-line assertion checking techniques are mostly used for detection and are complementary to IFRA in that such techniques can be efficiently used to generate posttriggers and also for fine-grained bug localization together with the post-analysis techniques supported by IFRA.

| Techniques             | Intrusive?         | Failure reproduction?       | System-level simulation? | Area<br>impact? | Applicability? |

|------------------------|--------------------|-----------------------------|--------------------------|-----------------|----------------|

| Formal methods         | (+) No             | (+) No<br>(-) Yes<br>(+) No | (+) No                   | (-) Yes         |                |

| Trace buffer           | Depends            |                             |                          |                 |                |

| Scan<br>methods        | (-) Yes<br>Depends |                             | (-) Yes                  | (+) SoC         |                |

| Clock<br>manipulation  |                    | (-) Yes                     |                          | (-) Yes         |                |

| Program & data tracing |                    |                             | () 100                   | (.) No.         |                |

| Checkpoint             | ())(               |                             |                          | (+) No          | (-) Processor  |

| & replay               | (-) Yes            |                             |                          |                 |                |

| Assertion<br>checking  | Depends            | Depends                     | (+) No                   | (-) Yes         | (+) SoC        |

| IFRA                   | (+) No             | (+) No                      | (+) No                   | (-) 1%          | (-) Processor  |

Table 2.5. IFRA vs. existing techniques.

## **2.6 CONCLUSIONS**

IFRA targets the problem of post-silicon bug localization of electrical bugs in a system setup, which is a major challenge in processor post-silicon design validation. Two major novelties of IFRA are:

- High-level abstraction for bug localization using low-cost hardware recorders that record semantic information about instruction data and control flows concurrently in a system setup, eliminating the need for failure reproduction.

- Special techniques, based on self-consistency, to analyze the recorded data for localization after failure detection without full system-level simulation.

However, IFRA has its own limitations, opening up several interesting research directions:

- The localization takes advantage of the structured architecture of processor designs, and targets bugs directly related to the core and not the cache logic or interfaces. Application of IFRA still needs to be extended to homogeneous / heterogeneous multi-core systems, and system-on-chips (SoCs) consisting of nonprocessor designs.

- IFRA does not currently support simultaneous multi-threaded processors [Shen 05].

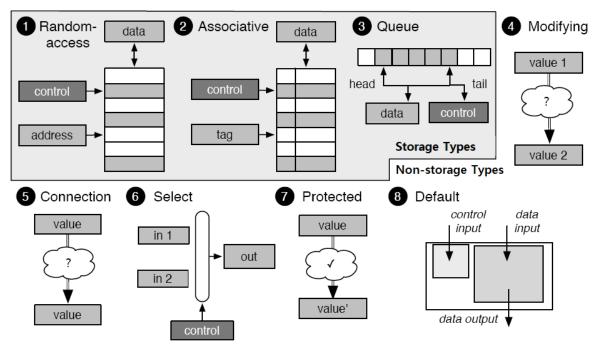

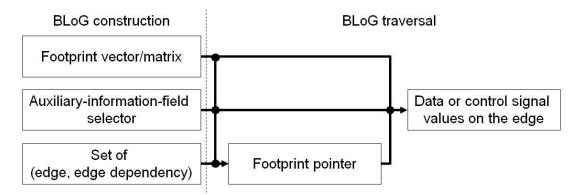

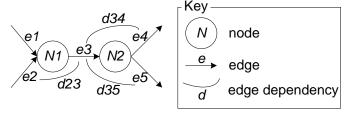

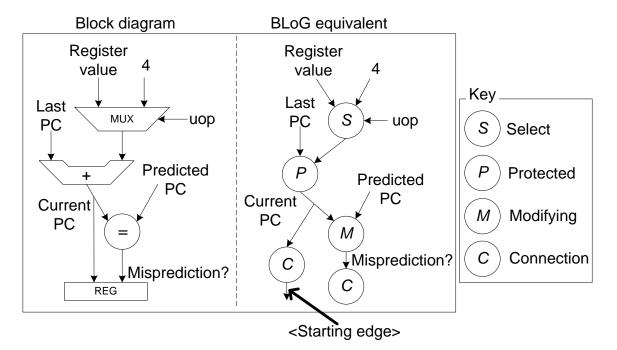

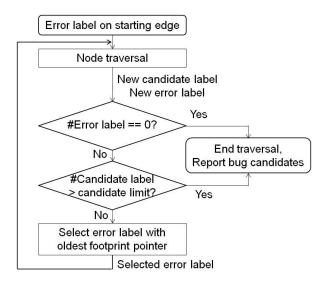

- Bugs that may only cause performance slowdown but not critical for correct program runs are not targeted.