# 127

## Improved GaAs Bonding Process for Quasi-Phase-Matched Second Harmonic Generation

Y. S. Wu and R. S. Feigelson

Department of Materials Science and Engineering, Stanford University, Stanford, California, USA

R. K. Route, D. Zheng, L. A. Gordon, M. M. Fejer, and R. L. Byer

Department of Applied Physics, Stanford University, Stanford, California, USA

### ABSTRACT

A multilayer stack of bonded GaAs wafers, each layer rotated 180° from the adjacent one, has been proposed for quasi-phase-matched second harmonic generation. Current bonding technology, however, often leads to unacceptable optical losses and, therefore, poor device performance. In this study, three sources of optical losses were investigated: (i) interfacial defects between the wafers, (ii) bulk defects within the wafers, and (iii) decomposition at the exposed outer surfaces. Surface losses due to incongruent evaporation were easily eliminated by repolishing the outer surfaces. However, to minimize the losses from interfacial and bulk defects, it was necessary to investigate the relationship between these defects and the processing parameters. It was found that an increase in temperature and/or time led to a decrease in interfacial defects, but an increase in bulk and surface defects. Optimized processing conditions were developed which permit the preparation of stacks containing over 50 layers of (100) GaAs wafers, and about 40 layers of (110) GaAs wafers. Optical losses as low as 0.1 to 0.3 % per interface (at 5.3 and 10.6  $\mu\text{m}$ ) were observed for the (110) oriented multilayer structures.

### Introduction

There is a need for mid-infrared (MIR) high-power coherent sources, especially in the 3 to 5  $\mu\text{m}$  region where atmospheric windows permit remote sensing and military countermeasures. These sources can be provided by nonlinear frequency conversion of existing lasers. However, currently available infrared (IR) nonlinear crystals such as  $\text{AgGaS}_2$ ,  $\text{AgGaSe}_2$ , and  $\text{ZnGeP}_2$  are limited by low surface damage thresholds, and challenging growth technologies. In contrast to these materials, GaAs has a large nonlinear coefficient, good MIR transmission, high thermal conductivity, and a high optical damage threshold. Moreover, GaAs crystal growth technology is well developed and high quality wafers are widely available. However, its use in nonlinear optical applications has been limited because GaAs, a cubic crystal, cannot be birefringently phase-matched.

An alternative to birefringent phase-matching is quasi-phase-matching,<sup>1</sup> where a periodic modulation of the nonlinear susceptibility compensates for the phase velocity mismatch between the interacting waves. Air-spaced stacks of GaAs plates at Brewster's angle have been used,<sup>2</sup> but optical losses at the air-GaAs interfaces proved to be excessive. To minimize these air-interfacial losses, Gordon et al.<sup>3</sup> proposed forming a periodic structure free of air-GaAs interfaces by a high temperature diffusion bonding process. For quasi-phase-matched second harmonic generation (QPM SHG) of a high power  $\text{CO}_2$  laser in which a second harmonic at 5.3  $\mu\text{m}$  is generated from a fundamental at 10.6  $\mu\text{m}$ , their calculations showed that a stack of approximately 50 or more (110)-oriented GaAs layers with optical losses of less than 0.2% per layer would be required for efficient frequency conversion. The principal goal of this research, therefore, has been to develop a bonding process capable of producing a stack of this size having low optical losses.

**Background.**—Wafer bonding, sometimes known as wafer fusion or diffusion bonding, has been used as an alternative to heteroepitaxy in electronic and optoelectronic devices. While most work has been done with silicon,<sup>4</sup> III-V semiconductors have been studied for two-layer optoelectronic devices.<sup>5,6</sup> In our program, we have built on these earlier two-layer results with the intent of producing a bulk periodic GaAs structure (a periodically twinned crystal) which cannot easily be generated by bulk crystal growth techniques.

The most significant problems encountered were excess optical losses caused by interfacial defects between the

wafers and bulk defects within individual wafers. Interfacial defects were found to consist essentially of voids and inclusions, caused by natural topographical irregularities (atomic scale surface roughness and/or long-range surface waviness), surface contamination (GaAs and/or other types of particles and surface oxides), and solvent residues or trapped gases between the wafers. The causes of bulk and surface defects are more complicated and it is well known from the extensive literature in the field that these include dislocations, impurities, vacancies, interstitials, precipitates, and antisite defects. Arsenic antisite defects (arsenic on gallium sites  $\text{As}_{\text{Ga}}$ ) and clusters of other defects are generally known as EL2 (a deep donor in GaAs),<sup>7</sup> the concentration of which increases with arsenic concentration in the crystal.<sup>8</sup> At typical bonding temperatures, the evaporation rate of arsenic from the surface is higher than that of gallium (about 2.5 times at 827°C),<sup>9</sup> which decreases the arsenic (and thus the EL2) concentration and converts the outer surface from semi-insulating to p-type. This conversion effect was thought to be a major factor responsible for the decrease in the transmittance of GaAs single wafers.<sup>10</sup>

In this research, the origins of scattering and absorption losses were investigated through a systematic study of bonding mechanisms and procedures, coupled with extensive materials and optical characterization.

### Experimental

**Sample preparation.**—The devices fabricated in this study were not suitable for practical SHG devices. They require (110)-oriented wafers with tightly controlled thickness equal to the optical coherent length of the specific nonlinear optical interaction of interest, (e.g., 106  $\mu\text{m}$  for first-order or 318  $\mu\text{m}$  for third-order doubling of a 10.6  $\mu\text{m}$   $\text{CO}_2$  laser<sup>3</sup>). Because we were interested in developing an effective GaAs bonding process, readily available wafers in standard thicknesses were chosen. Undoped semi-insulating (100) and (110) GaAs wafers, from Atramec Inc., polished on both sides were used in this study. Wafers were 3 in. in diameter, had etch pit densities less than  $10^5 \text{ cm}^{-2}$ , and thicknesses of 630  $\mu\text{m}$  for the (100)-oriented wafers and 500  $\mu\text{m}$  for the (110)-oriented wafers. To assure that p-type conversion was minimized, the resistivities of these wafers ( $\sim 10^8 \Omega\text{-cm}$ ) were guaranteed by the vendor to be stable after annealing at 850°C in either an arsenic over-pressure or under a plasma-enhanced chemical vapor deposition (PECVD)  $\text{Si}_3\text{N}_4$  cap for 0.5 h.

The atomic scale surface roughness of these as-received wafers (over a  $5 \times 5 \mu\text{m}$  area) was measured using atomic force microscopy (AFM). Surfaces were very smooth with a typical peak-to-valley distance of only 1 nm. The surface waviness (long range flatness) in a  $1 \times 1 \text{ cm}$  area was measured with a profilometer (Dektak IIA). The center of each wafer was generally much flatter than the periphery (edge), as expected. The peak-to-valley waviness at the center of a GaAs wafer was  $< 100 \text{ nm}$ , while that around the periphery was  $\approx 300 \text{ nm}$ .

Wafers were diced into  $9 \times 9 \text{ mm}$  samples with a diamond saw, then solvent-cleaned in a class 100 clean room using a series of deionized water, boiling trichlorethane 1-1-1 (TCA), boiling acetone, and boiling isopropyl baths. (No effort was made to remove the surface oxide layer by chemical etching.) Finally, the specimens were dried in a stream of nitrogen gas. For these studies, only samples from the flatter central portions of the wafers were used.

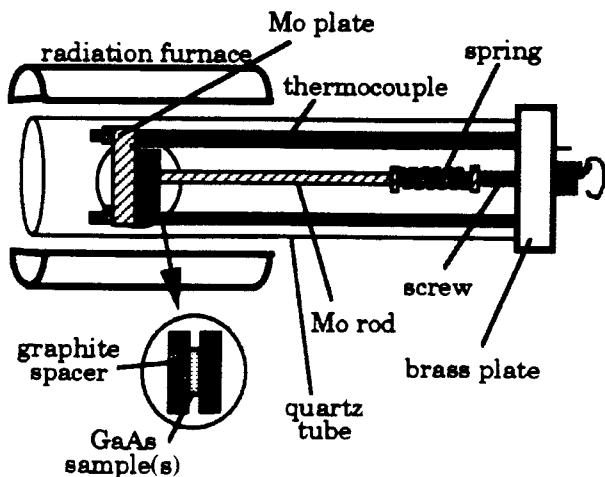

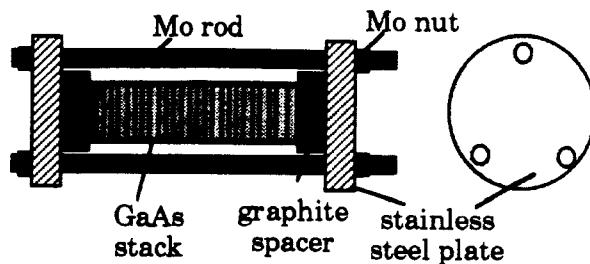

**Heat-treatment/bonding procedures.**—The cleaned GaAs samples were stacked in an inert refractory sample holder made of high purity graphite with molybdenum structural components. Bonding was carried out in a lamp-heated furnace (shown in Fig. 1) to permit rapid thermal cycling. A transparent atmosphere control quartz tube (chamber), which could be sealed and backfilled with  $\text{H}_2$  and  $\text{N}_2$  at pressures from  $10^{-3}$  Torr to 1 atm, was used to prevent oxidation of the GaAs stacks during heat-treatment. The compressive load on the GaAs sample could be adjusted to as high as  $30 \text{ kg/cm}^2$  with a spring-loaded screw at the end of the sample holder. For large multilayer stacks, 52 wafers of (100) GaAs and 39 wafers of (110) GaAs, a differential thermal expansion fixture, Fig. 2 (containing stainless steel, molybdenum, and graphite), was used because the spring-loaded fixture could not accommodate such large specimens. These tall GaAs stacks were clamped at room temperature with only a minimal applied compressive load. On heating to the processing temperature, the compressive stress on the GaAs stack increased due to differential thermal expansion between the various materials making up the sample holder. The actual compressive stresses achieved with the differential thermal expansion fixture could not be determined by calculation because both the GaAs and the holder underwent plastic deformation at some temperature during the process cycle.

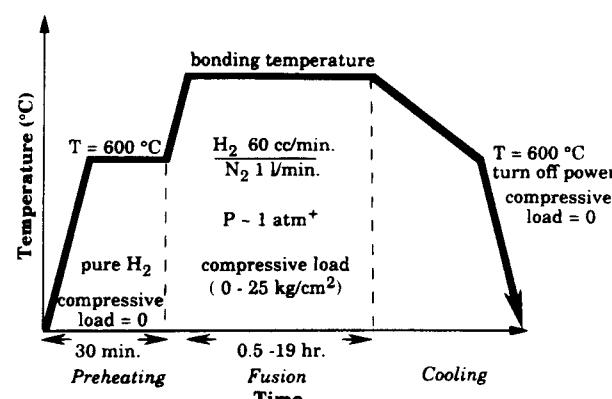

Figure 3 illustrates a typical GaAs bonding cycle. It included three-steps: preheating, bonding, and cooling. In the first step, the chamber was evacuated to 15 mTorr at room temperature, then backfilled with ultrahigh pure  $\text{H}_2$  to 50 Torr. The GaAs samples were then heated to  $600^\circ\text{C}$ , at a rate of  $20^\circ\text{C}/\text{min}$  (without applying a compressive load, but with repeated evacuation and backfilling). The compressive load (typically  $10 \text{ kg/cm}^2$ ) was then applied,

Fig. 1. Radiation furnace used for GaAs bonding.

Fig. 2. Differential thermal expansion fixture for clamping multi-layer GaAs stacks in the bonding furnace.

and the chamber was backfilled with a gas mixture of  $\text{H}_2$  and  $\text{N}_2$  up to 760 Torr (1 atm). Under a flowing gas mixture of  $\text{H}_2$  ( $60 \text{ cm}^3/\text{min}$ ) and  $\text{N}_2$  ( $1,000 \text{ cm}^3/\text{min}$ ) in a purge mode, any additional heating was continued (at the rate of  $30^\circ\text{C}/\text{min}$ ) until the desired bonding temperature was reached. After a period of 2 to 20 h, the furnace was cooled at the rate of  $10^\circ\text{C}/\text{min}$ . The compressive load was released at  $600^\circ\text{C}$  and the furnace power turned off. This process sequence was found to minimize the amount of optical scattering at the interfaces caused by interface contamination, and it led to reasonably good optical transmittance.

A few bonding experiments were also carried out at temperatures below  $600^\circ\text{C}$ .

**Sample geometry.**—Three types of GaAs structures were used for process optimization: (i) single GaAs wafers, (ii) simple two-layer stacks, and (iii) two-layer stacks with artificial interfacial voids. The single GaAs wafers were processed under identical thermal conditions and were used to separate the bulk and surface effects, from the interfacial effects. The study of samples containing artificial voids followed the approach described in Ref. 11. It involved the creation of controlled voids in one wafer surface by etching photolithographically generated patterns with a solution of  $\text{H}_2\text{SO}_4$ ,  $\text{H}_2\text{O}_2$ , and  $\text{H}_2\text{O}$ , and then bonding it to an unpatterned wafer. Using this approach, we were able to vary the void depth and therefore simulate the interfacial defects which are caused by natural topographical irregularities on the wafer surface.

From these experiments on one- and two-layer samples an optimized process was developed. This process was then used to bond multilayer stacks [a 52-layer stack of (100) GaAs wafers and a 39-layer stack of (110) GaAs wafers].

**Characterization.**—The transmittance of individual wafers and multilayer structures was measured by means of Fourier transform infrared (FTIR) spectroscopy (BIO-

Fig. 3. The typical GaAs bonding cycle used in this experiment. The heating rate was  $30^\circ\text{C}/\text{min}$  and the cooling rate  $10^\circ\text{C}/\text{min}$ .

αAD FTS-40) with a beam size of 4 mm diam. The electrical behavior was determined from four-point probe, hot probe, and Hall effect measurements. The samples containing artificial voids at the wafer interface were characterized by infrared (IR) transmission optical microscopy and the interfaces were analyzed by high resolution transmission electron microscopy (HRTEM) (CM20 Philips).

## Results and Discussion

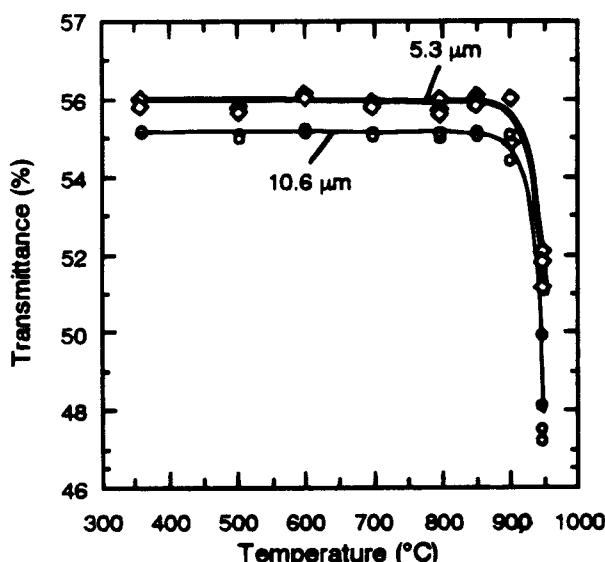

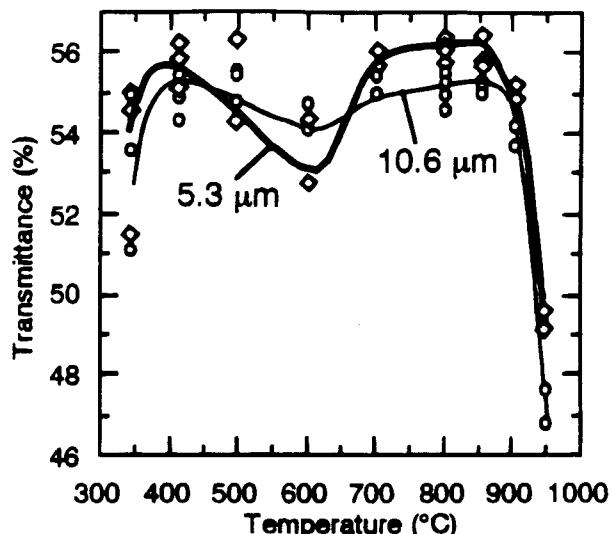

**Bulk and surface defects in single GaAs wafers.**—Figure 4 shows the transmittance of single GaAs wafers heat-treated for 2 h at temperatures between 350 and 950°C. When compared with an unprocessed GaAs wafer, the optical losses are seen to increase when processing temperatures exceed 850°C at the two wavelengths of interest for SHG. Since there is no interface in single-wafer experiments, these losses must have been caused by bulk and surface defects. The electrical properties also changed when the processing temperatures exceeded 850°C. Undoped semi-insulating wafers converted to p-type and their sheet resistance decreased at progressively higher temperatures. This increase in free carrier concentration is thought to be the major cause of the optical losses (free carrier absorption) seen in the two-layer stacks at temperatures over 850°C (Fig. 5). Since the loss of arsenic is the major cause of p-type conversion, we have found that thermal degradation can be significantly reduced by replacing the conventional porous graphite holder with nonporous pyrolytic graphite.<sup>12</sup>

It was also found that the optical transmission and sheet resistance increased with processing time. At 850°C, the sheet resistance decreased from  $1 \times 10^5$  to  $5 \times 10^3 \Omega/\square$ , as the bonding time was increased from 2 to 11 h. However, the optical transmission and sheet resistance could be restored to their preprocessing levels after 2 μm of each surface was removed by polishing.

Surface polishing also affected the optical and electrical properties of single GaAs wafers processed at 950°C for 2 h. The optical transmission and sheet resistance were measured before and after 5 and 9 μm had been removed from each surface. The optical transmission increased when the surface layer was removed. When 9 μm was polished away, the transmission spectra became closer to that of the unprocessed single wafers. On the other hand, while the sheet resistance increased from  $10 \Omega/\square$  (surface layer intact) to  $5 \times 10^2 \Omega/\square$  (with 5 μm surface removed) and to  $10^3 \Omega/\square$  (with 9 μm surface removed), the sheet resistance did not recover its original value ( $10^6 \Omega/\square$ ).

Fig. 4. Transmittance of single GaAs (100) wafers processed under a static  $10 \text{ kg/cm}^2$  load for 2 h at different temperatures ranging from 350 to 950°C.

Fig. 5. Transmittance of two-layer bonded GaAs (100) wafers processed under a static  $10 \text{ kg/cm}^2$  load for 2 h at different temperatures ranging from 350 to 950°C.

The observed degradation in optical transmission (thermal conversion) was found to depend both on the manufacturing processing history of the as received commercial GaAs wafers and on the processing conditions used. Using a similar process, Zheng et al.<sup>13</sup> found that transmittance decreased at temperatures as low as 700°C. In this study, the wafers were stable to 850°C. The GaAs wafers used in both our research and Ref. 13 were undoped, semi-insulating material purchased from the same vendor, but they came from different boules. This variability led to the necessity of developing a tighter set of specifications, (the high-temperature stability of the wafer resistivity) for qualifying commercial wafers for this QPM application.

Other factors which are known to affect optical transmission include: (i) the plastic deformation of GaAs under a fixed compressive load (increase with temperature<sup>14</sup>) which can introduce optical distortions through a strain birefringence mechanism, and (ii) the inward diffusion of mobile impurities from the wafer surfaces. Since the diffusion constant of carbon (a shallow acceptor in GaAs) is very small,<sup>15</sup> the graphite holder is expected to have little effect on optical loss. On the other hand, iron from the stainless steel components could affect optical transmission, even though iron itself was not in direct contact with the GaAs. Defects such as these would be expected to have a deleterious effect on the optical properties and possibly be responsible for the slight optical absorption detected even after the defective As-depleted surfaces (surface defects) had been polished away.

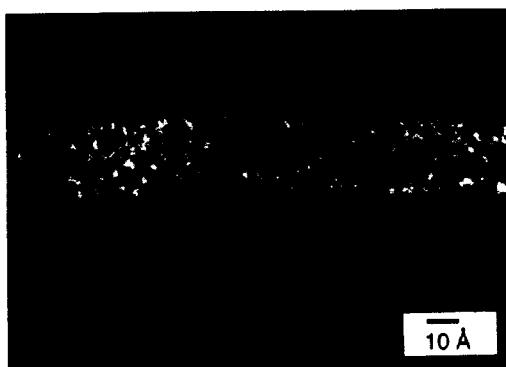

**Two-layer bonding.**—Figure 5 shows the transmittance of simple two-layer GaAs stacks bonded at temperatures between 350 and 950°C for 2 h. We found that GaAs does not bond at temperatures below 300°C. A more or less continuous increase in optical transmission was expected with increasing bonding temperature, since mass transport (diffusion, vapor transport, etc.) increases with temperature. However, at both 5.3 and 10.6 μm wavelengths, two maxima in optical transmittance were observed at bonding temperatures of 410 and 850°C, and a pronounced drop was observed at intermediate temperatures. TEM analysis of these specimens revealed that two different mechanisms were involved. At 410°C, GaAs does not bond directly to itself, but via an amorphous oxide layer, as shown in Fig. 6. The presence of this oxide layer is not surprising, since the native surface oxides were not removed in the cleaning process. When processed at 850°C, GaAs was found to be bonded directly to itself, as shown in Fig. 7. This behavior is consistent with GaAs IC processing tech-

Fig. 6. Cross-sectional high resolution TEM of GaAs (100) interface bonded at 410°C, showing oxide layer at interface.

nology in which it is well known that native oxides on GaAs volatilize at temperatures around 500°C.<sup>16</sup>

In related studies, Hjort et al.<sup>17</sup> bonded (100) GaAs wafers between 400 and 900°C without an applied compressive load and characterized them by IR image and interface fracture energy measurement. They also found that GaAs could be successfully bonded at temperatures around 410°C due to oxide at the interface, but as the bonding temperatures increased, the fraction of well-bonded areas (measured by "IR image" method) decreased. We believe the observed decrease in the fraction of well-bonded areas in their experiments was the result of deterioration of the oxide bonding layer due to volatilization of the native surface oxide. In contrast to our studies, in which optical transmission of bonded layers began to increase at temperature over 600°C, the fraction of well-bonded areas in the Hjort et al. samples did not. The major difference in the processing used in these two studies is that in our case, the samples were under a compressive load. We found that bonding (as measured by optical transmission) improved with applied compressive load in the 1 to 30 kg/cm<sup>2</sup> range at a bonding temperature of 850°C. In other words, the higher the pressure on the two-layer stacks, the better the optical transmission.

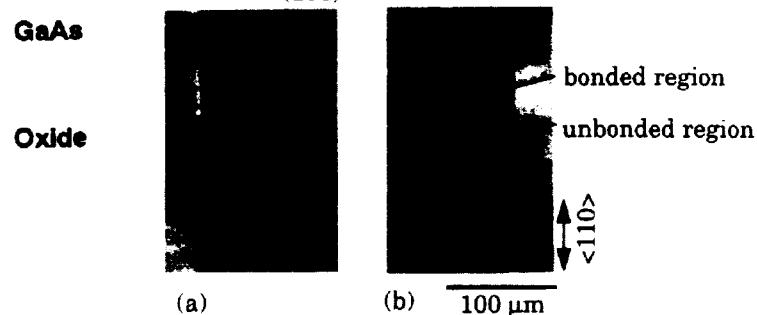

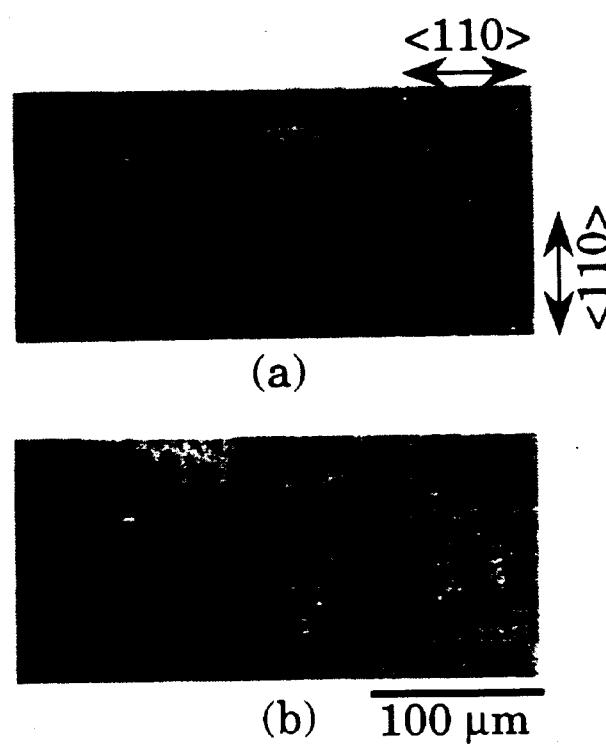

*Two-layer bonding with artificial interfacial voids.*—Figure 8 shows IR transmission optical micrographs for two wafers containing 700 Å deep artificial voids that were bonded at 870 and 910°C for 2 h. The light features seen in the void area of Fig. 8b correspond to bonded areas created by the nucleation of crystallites and mass transport within the void space. The nature of the bonding in these regions was verified using HRTEM, like that shown in Fig. 7. No other phases were found at the bonded interfaces, and only a few atomic layers were disrupted. Even though a native oxide layer is likely to have formed on the wafer surfaces before they were loaded into the furnace,

Fig. 8. IR transmission optical microscope images of interfacial voids (originally 700 Å deep) on GaAs (100) wafers after bonded at temperatures of (a) 870 and (b) 910°C for 2 h.

the results from the previous section indicate that complete reduction/volatilization should have occurred under these bonding conditions, and, in fact, no oxygen was detected in the interface region by EDAX analysis.

The bonding fraction, as determined by estimating the light versus dark areas on the IR transmission micrographs, was found to increase with temperature, consistent with the fact that mass transport increases with temperature.<sup>18</sup> We found that the detectable bonding fraction was affected by the void depth. Bonding (or recrystallization) was not detected in 700 Å deep voids until the process temperatures reached 910°C, as shown in Fig. 8. However, it was detected in 100 Å deep voids at temperatures around 850°C, as shown in Fig. 9. The fraction also increased slowly with time, as expected from the kinetic nature of the process. These experiments showed that the bonding fraction in GaAs wafers depends strongly on the magnitude of the height of the surface irregularities at the wafer interfaces as well as temperature and time. Similar conclusions were drawn by Rodé and Glaeser<sup>11</sup> during bonding studies of sapphire wafers.

Fig. 7. Cross-sectional high resolution TEM of GaAs (100) interface bonded at 850°C, showing intimate contact between GaAs plates with no intervening oxide layer.

Fig. 9. IR transmission optical micrograph of artificial voids (originally 100 Å depth) in GaAs (100) wafers bonded at 850°C for: (a) 2.5 and (b) 7.5 h.

**Multilayer bonding.**—The interfacial, bulk, and surface defect studies described above clearly showed that higher temperatures and longer times led to an increase in the bonding fraction (i.e., a decrease in interfacial defects), but they also led to an increase in the density of surface and bulk defects. Figure 4 shows that the transmittance of a single GaAs wafer, heat-treated at 850°C for 2 h was, within experimental error (1%), the same as that of an unprocessed GaAs wafer. For these wafers, the optical losses due to bulk and surface defects introduced by processing at 850°C were very small. At the same time, the study of interfacial defects using two-wafer stacks showed that the bonding fraction on a flat surface with 100 Å deep voids was reasonably high at a temperature of 850°C (Fig. 9). It can also be seen from Fig. 5 that the transmittance of two-layer stacks free of artificial voids is high at 850°C. For this reason, a temperature of 850°C was selected as the best temperature for bonding multilayer stacks for nonlinear optical devices.

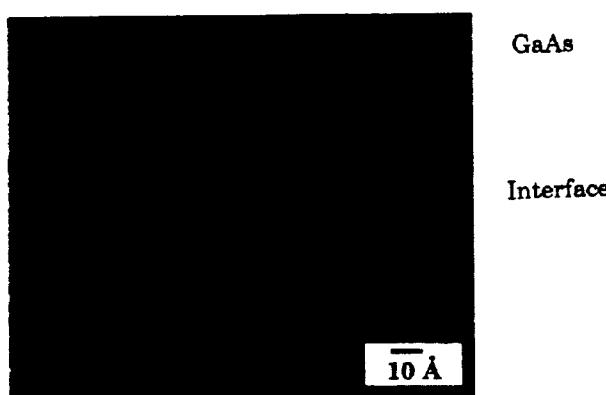

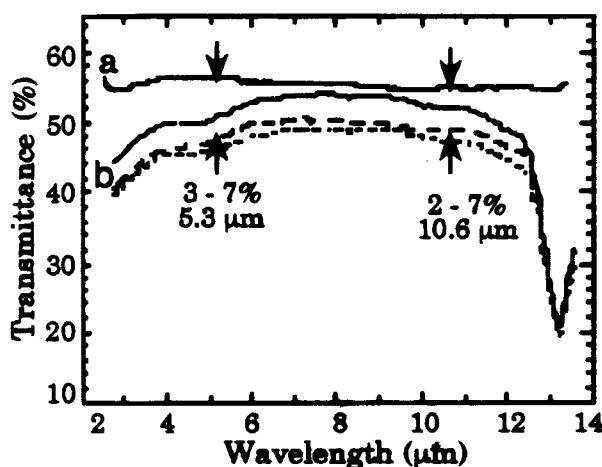

A 52 layer (100)-oriented stack, of 630  $\mu\text{m}$  thick wafers, was bonded at 850°C, for 0.5 h (a somewhat shorter interval than used in the two-layer studies). The average optical losses per layer were 0.9% at 5.3  $\mu\text{m}$  and 0.5% at 10.6  $\mu\text{m}$ . Following these experiments, a stack of 39 (110)-oriented wafers, each 500  $\mu\text{m}$  thick, was bonded under the same conditions. The average optical losses per layer were even lower, 0.1–0.3% at both 5.3 and 10.6  $\mu\text{m}$ , as shown in Fig. 10. The reduced in optical losses in the 39 layer stack may have come from the reduction of wafer thickness (shorter absorption pathlength), from 630 to 500  $\mu\text{m}$ , and/or the different properties (mechanical, physical, and chemical) of the different wafer surface orientations, (100) versus (110).

The optical losses achieved in these studies are considered low enough for practical devices, and we believe continued experiments with custom-fabricated GaAs wafers prepared to the thickness required for specific optical interactions are warranted. Such studies are currently under way.

### Conclusions

An investigation of the relationship between bonding conditions (temperature, time, and pressure) and optical loss (resulting from bulk, interfacial, and surface defects), has led to the development of a simple, effective process for preparing periodic GaAs structures useful in quasi-phase-matched second harmonic generation applications. It was found that bulk optical losses caused by plastic deformation, can be minimized by applying a more uniform and limited pressure to the wafer stacks during bonding. It was also found that interfacial defects, in the form of inclusions and voids can be minimized by improving wafer cleanliness, smoothness, and bonding condi-

tions. In the case of interfacial voids, (which are inevitable because atomically smooth wafers are not available), these can be significantly reduced by (i) increasing the compressive pressure at a given bonding temperature or (ii) increasing the bonding temperature and time. If the pressure is too high, however, plastic deformation results and bulk optical losses will increase. When the temperature and time at temperature are increased, bulk defects and surface evaporation also increase to produce higher losses. The problem associated with evaporation from the external surfaces during bonding (caused by arsenic depletion resulting from incongruent evaporation) can be easily eliminated by repolishing after heat treatment.

The process developed in this study involves the use of a relatively uniform pressure and moderately high temperatures (850°C) to produce optimal results. Using this procedure it was possible to fabricate optical stacks of (110)-oriented wafers in which the optical losses were low enough for practical nonlinear optical devices.

For QPM SHG of the 10.6  $\mu\text{m}$  CO<sub>2</sub> laser, the first and third order coherence lengths are 106 and 318  $\mu\text{m}$ , respectively.<sup>3</sup> We anticipate that stacks fabricated from wafers of these thicknesses will exhibit even lower bulk optical absorption losses due to their reduced optical path lengths. Additional reductions in optical losses are also expected through fine-tuning of the processing parameters, and through the use of postannealing processing under arsenic overpressures.

### Acknowledgments

This project was funded by DARPA through the Center for Nonlinear Optical Materials at Stanford University and by the Army Research Office, and has benefited from facilities and equipment made available to Stanford University by the NSF-MRSEC Program through the Center for Materials Research at Stanford University.

The authors would like to thank A. D. Marshall for TEM analysis.

Manuscript submitted April 25, 1997; revised manuscript received September 17, 1997.

Stanford University assisted in meeting the publication costs of this article.

### REFERENCES

1. A. Armstrong, N. Bloembergen, J. Ducuing, and P. S. Pershan, *Phys. Rev.*, **127**, 1918 (1962).

2. D. E. Thompson, J. D. McMullen, and D. B. Anderson, *Appl. Phys. Lett.*, **29**, 113 (1976).

3. L. A. Gordon, G. L. Woods, R. C. Eckardt, R. K. Route, R. S. Feigelson, M. M. Fejer, and R. Byer, *Electron. Lett.*, **29**, 1942 (1993).

4. W. P. Maszara, *This Journal*, **138**, 341 (1991).

5. F. A. Kish, D. A. Vanderwater, M. J. Peanasky, M. L. Ludowise, S. G. Hummel, and S. J. Rosner, *Appl. Phys. Lett.*, **67**, 2060 (1995).

6. Z. L. Liau and D. E. Mull, *ibid.*, **56**, 737 (1990).

7. O. Oda, H. Yamamoto, M. Seiwa, G. Kano, T. Inoue, M. Mori, H. Shimakura, and M. Oyake, *Semicond. Sci. Technol.*, **7**, A215 (1992).

8. D. E. Holmes, R. T. Chen, K. R. Elliot, C. G. Kirkpatrick, and P. H. Wu, *IEEE Trans. Electron Devices*, **ED-29**, 1045 (1982).

9. C. T. Foxton, J. A. Harvey, and B. A. Joyce, *J. Phys. Chem. Solids*, **34**, 1693 (1973).

10. R. Braunstein and L. Magid, *Phys. Rev.*, **111**, 480 (1958).

11. J. Rodel and A. M. Glaeser, *J. Am. Ceram. Soc.*, **73**, 592 (1990).

12. Y. S. Wu, R. S. Feigelson, R. K. Route, D. Zheng, L. A. Gordon, M. M. Fejer, and R. Byer, *Appl. Phys. Lett.*, Submitted.

13. D. Zheng, L. A. Gordon, Y. S. Wu, R. K. Route, M. M. Fejer, R. S. Feigelson, and R. L. Byer, Presented at the First Sino-American Workshop on Microstructured Crystals for Nonlinear Optics and Related Fields, April 1996.

14. S. Guruswamy, R. S. Rai, K. T. Faber, and J. P. Hirth, *J. Appl. Phys.*, **62**, 4130 (1987).

Fig. 10. Observed transmittance of (a) an unprocessed single GaAs wafer, and (b) a 39 layer stack of (110) bonded GaAs wafers at three different positions.

15. B. T. Cunningham, L. J. Guido, J. E. Baker, J. S. Major, Jr., N. Holonyak, Jr., and G. E. Stillman, *Appl. Phys. Lett.*, **55**, 687 (1989).

16. K. Tone, M. Yamada, Y. Ide, and Y. Katayama, *Jpn. J. Appl. Phys.*, **31**, L721 (1992).

17. K. Hjort, F. Ericson, J. A. Schweitz, C. Hallin, and E. Janzen, *This Journal*, **141**, 3242 (1994).

18. S. K. Ghandhi, *VLSI Fabrication Principles-Silicon and Gallium Arsenide*, 2nd ed., p. 197, Wiley, New York (1994).

Reprinted from JOURNAL OF THE ELECTROCHEMICAL SOCIETY

Vol. 145, No. 1, January 1998

Printed in U.S.A.

Copyright 1998